3.3.24 New Data 2 Register (M_CAN_NDAT2)

Address: 0h base + 9Ch offset = 9Ch

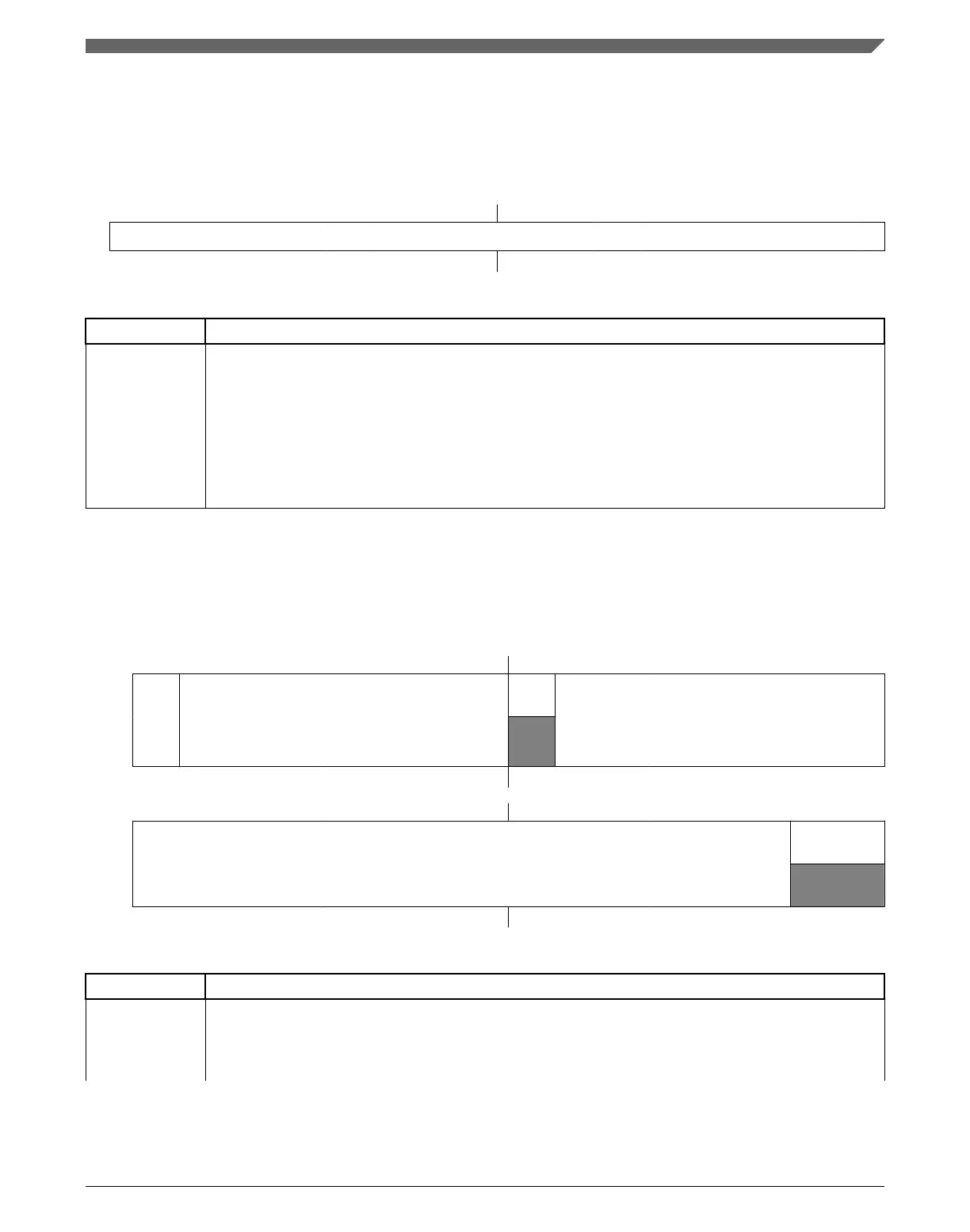

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

ND2

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

M_CAN_NDAT2 field descriptions

Field Description

0–31

ND2

New Data[32:63]

The register holds the New Data flags of Rx Buffers 32 to 63. The flags are set when the respective Rx

Buffer has been updated from a received frame. The flags remain set until the CPU clears them. A flag is

cleared by writing a 1 to the corresponding bit position. Writing a 0 has no effect. A hard reset will clear the

register.

0 Rx Buffer not updated

1 Rx Buffer updated from new message

3.3.25 Rx FIFO 0 Configuration Register (M_CAN_RXF0C)

Address: 0h base + A0h offset = A0h

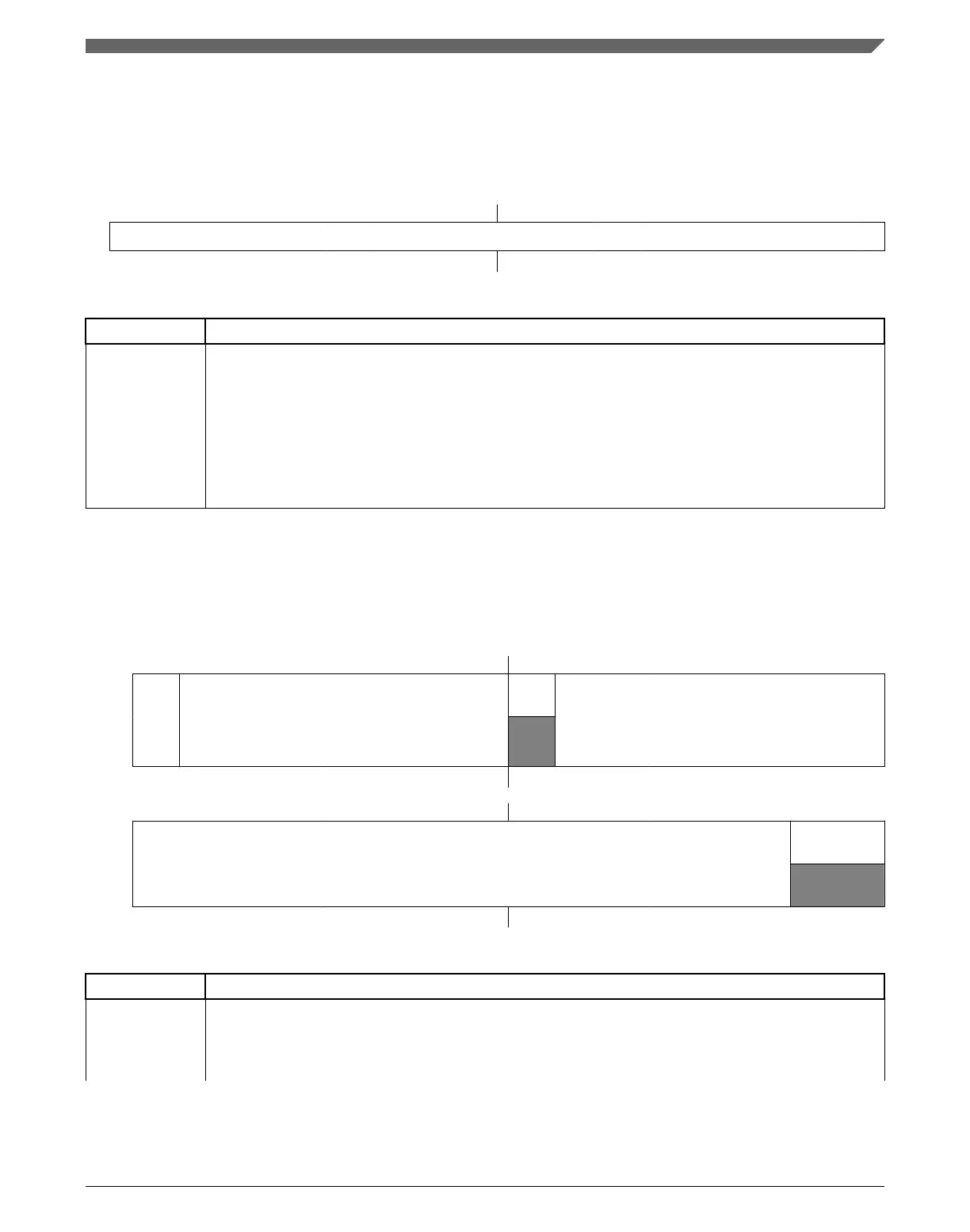

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R

F0OM

F0WM

0

F0S

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bit

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

F0SA

0

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

M_CAN_RXF0C field descriptions

Field Description

0

F0OM

FIFO 0 Operation Mode

FIFO 0 can be operated in blocking or in overwrite mode (see Rx FIFOs).

NOTE: This field has Protected Write status.

Table continues on the next page...

Chapter 3 Modular CAN (M_CAN)

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 61

Loading...

Loading...