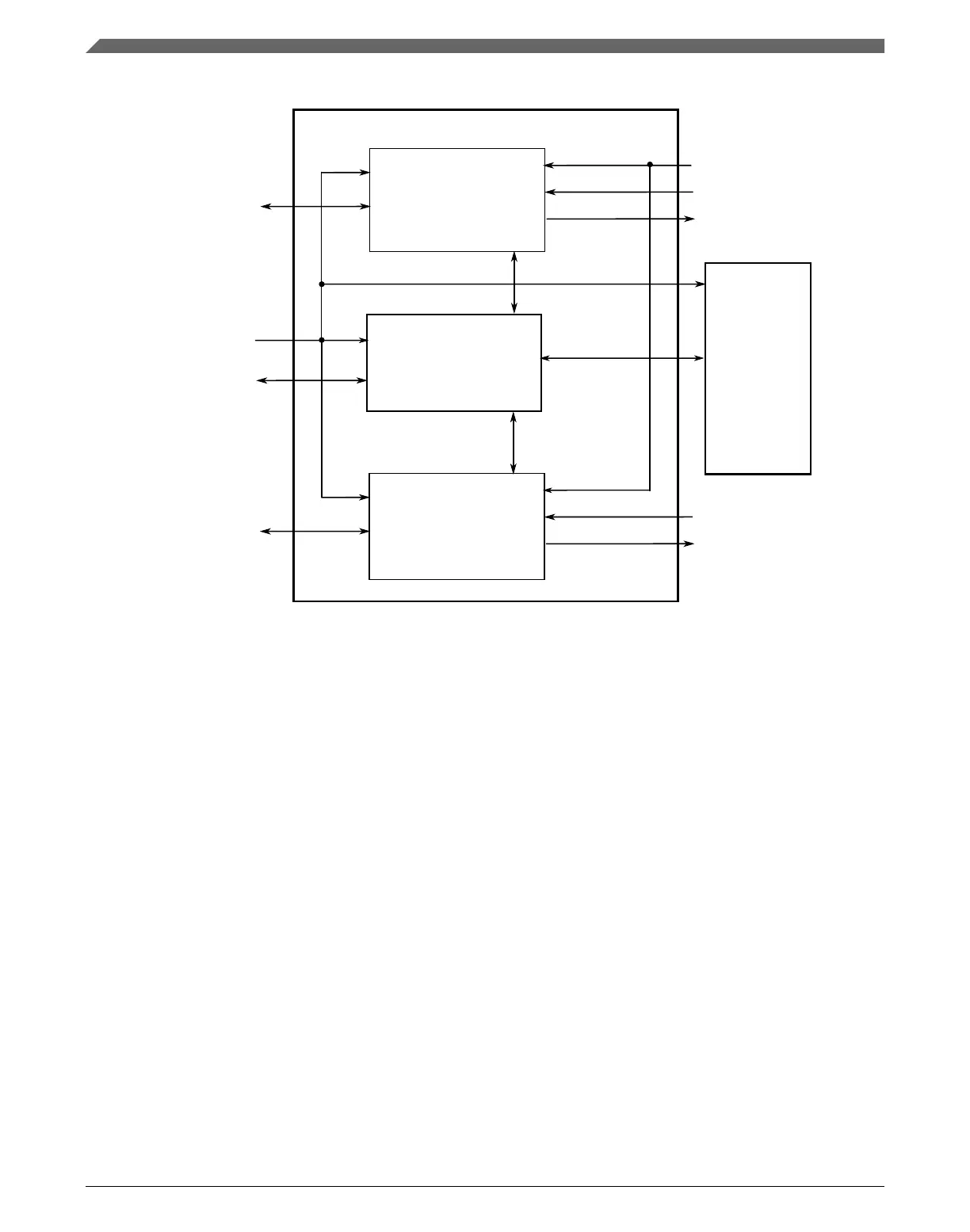

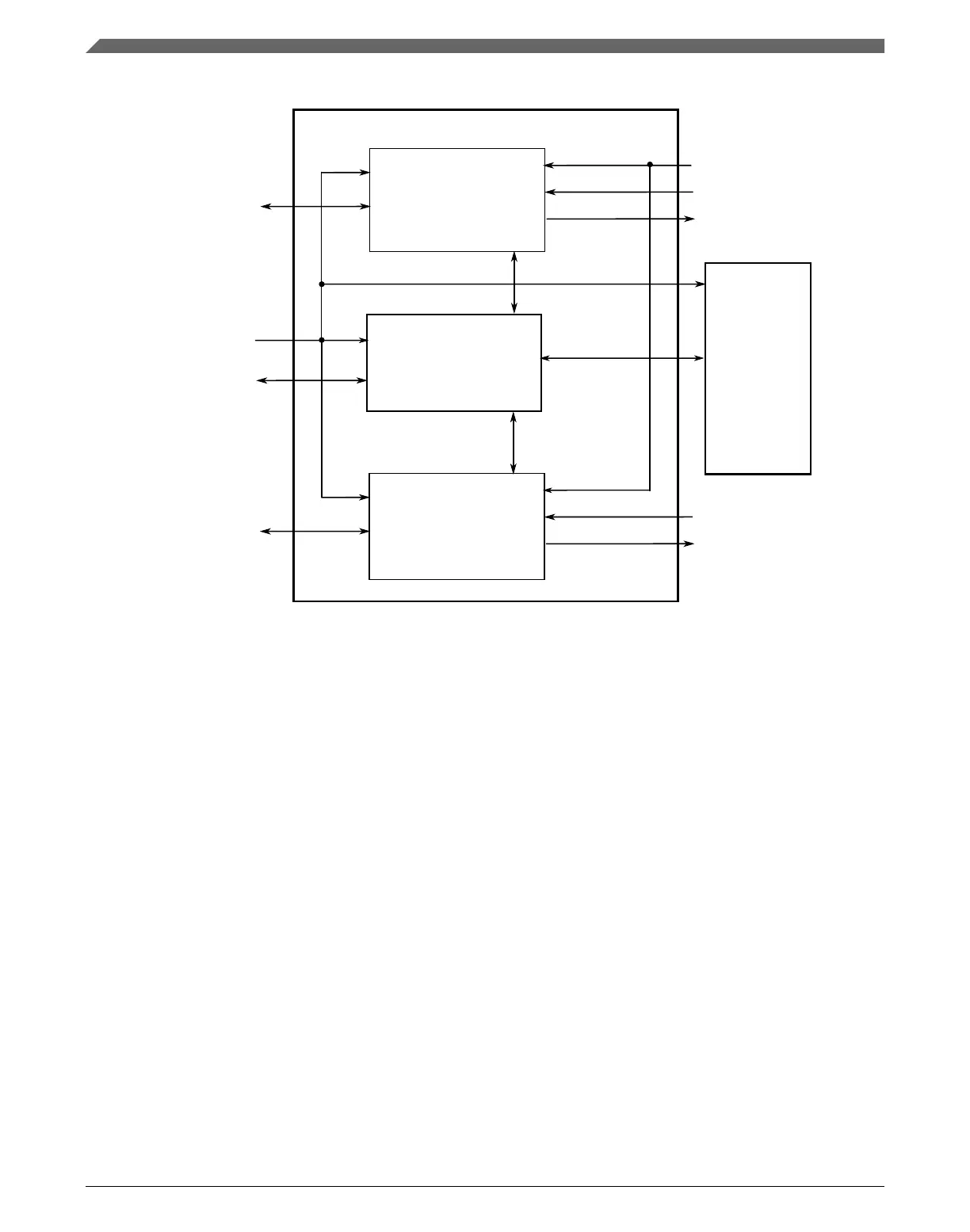

M _C A N_0

host clock

M_CAN_0_Rx

M_CAN_0_Tx

CAN protocol clock

Message RAM

Controller

External

Message

RAM

CPU reads/writes

CPU reads/writes

M_CAN Subsystem

CPU clock*

M _C A N_1

host clock

M_CAN_1_Rx

M_CAN_1_Tx

CPU reads/writes

*Refer to the Clocking chapter for M_CAN clock details.

Figure 3-1. M_CAN subsystem block diagram

3.1.3 Functional Description

3.1.3.1 Message RAM Controller

The Message RAM Controller has the arbiter for the accesses to the external Message

RAM and the ECC (Error Code Correction) Controller for the external Message RAM

data.

3.1.3.1.1 Message RAM Arbiter

The Message RAM Arbiter is a dynamic round robin arbiter that selects which request is

sent to the external Message RAM. These requests are made by the CPU, M_CAN_0, or

M_CAN_1.

This arbiter ensures:

Chip-specific M_CAN information

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

20 Freescale Semiconductor, Inc.

Loading...

Loading...