M_CAN_TSCV field descriptions

Field Description

0–15

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

16–31

TSC

Timestamp Counter

The internal Timestamp Counter value is captured on start of frame (both Rx and Tx). When TSCC[TSS] =

01, the Timestamp Counter is incremented in multiples of CAN bit times [1…16] depending on the

configuration of TSCC[TCP]. A wrap around sets interrupt flag IR[TSW]. Write access resets the counter

to zero.

NOTE: A "wrap around" is a change of the Timestamp Counter value from non-zero to zero not caused

by write access to TSCV.

3.3.10 Timeout Counter Configuration Register (M_CAN_TOCC)

See Timeout Counter for a description of the Timeout Counter or for use of timeout

function with CAN FD.

Address: 0h base + 28h offset = 28h

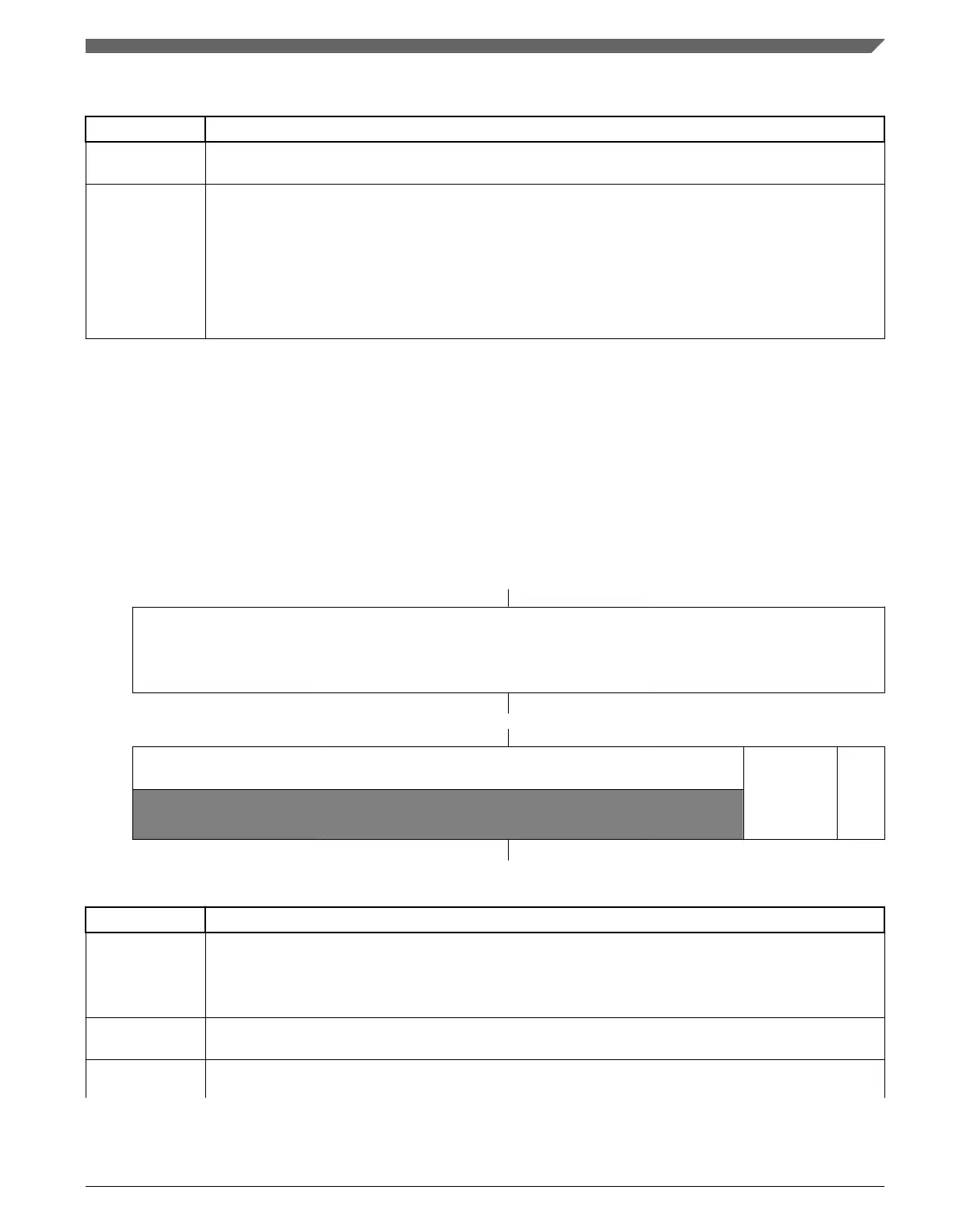

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R

TOP

W

Reset

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Bit

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

0

TOS

ETOC

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

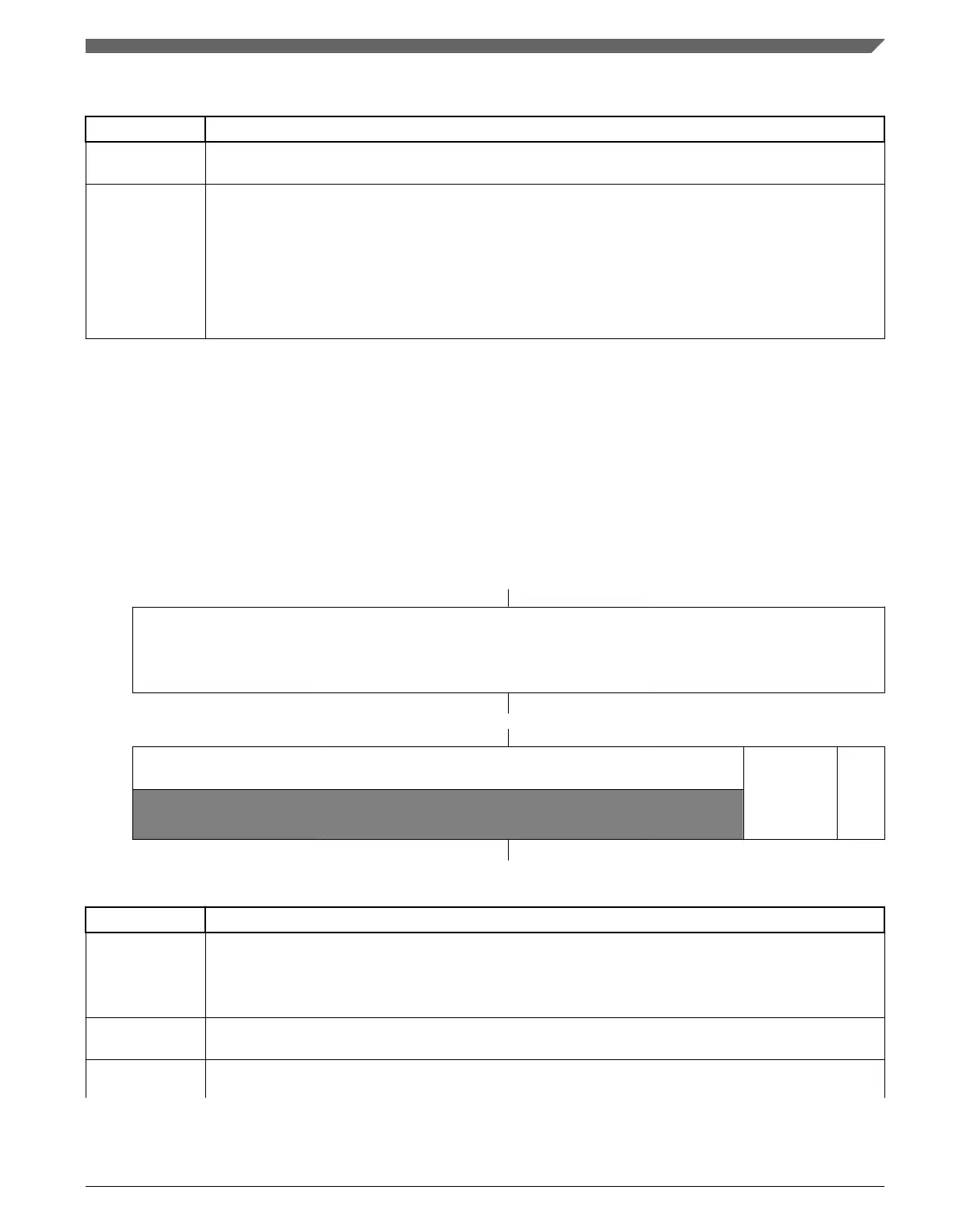

M_CAN_TOCC field descriptions

Field Description

0–15

TOP

Timeout Period

Start value of the Timeout Counter (down-counter). Configures the Timeout Period.

NOTE: This field has Protected Write status.

16–28

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

29–30

TOS

Timeout Select

Table continues on the next page...

Chapter 3 Modular CAN (M_CAN)

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 39

Loading...

Loading...