M_CAN_TXBCR field descriptions

Field Description

0–31

CR

Cancellation Request

Each Tx Buffer has its own Cancellation Request bit. Writing 1 will set the corresponding Cancellation

Request bit; writing 0 has no impact. This enables the CPU to set cancellation requests for multiple Tx

Buffers with one write to TXBCR. TXBCR bits are set only for those Tx Buffers configured via TXBC. The

bits remain set until the corresponding bit of TXBRP is reset.

0 No cancellation pending

1 Cancellation pending

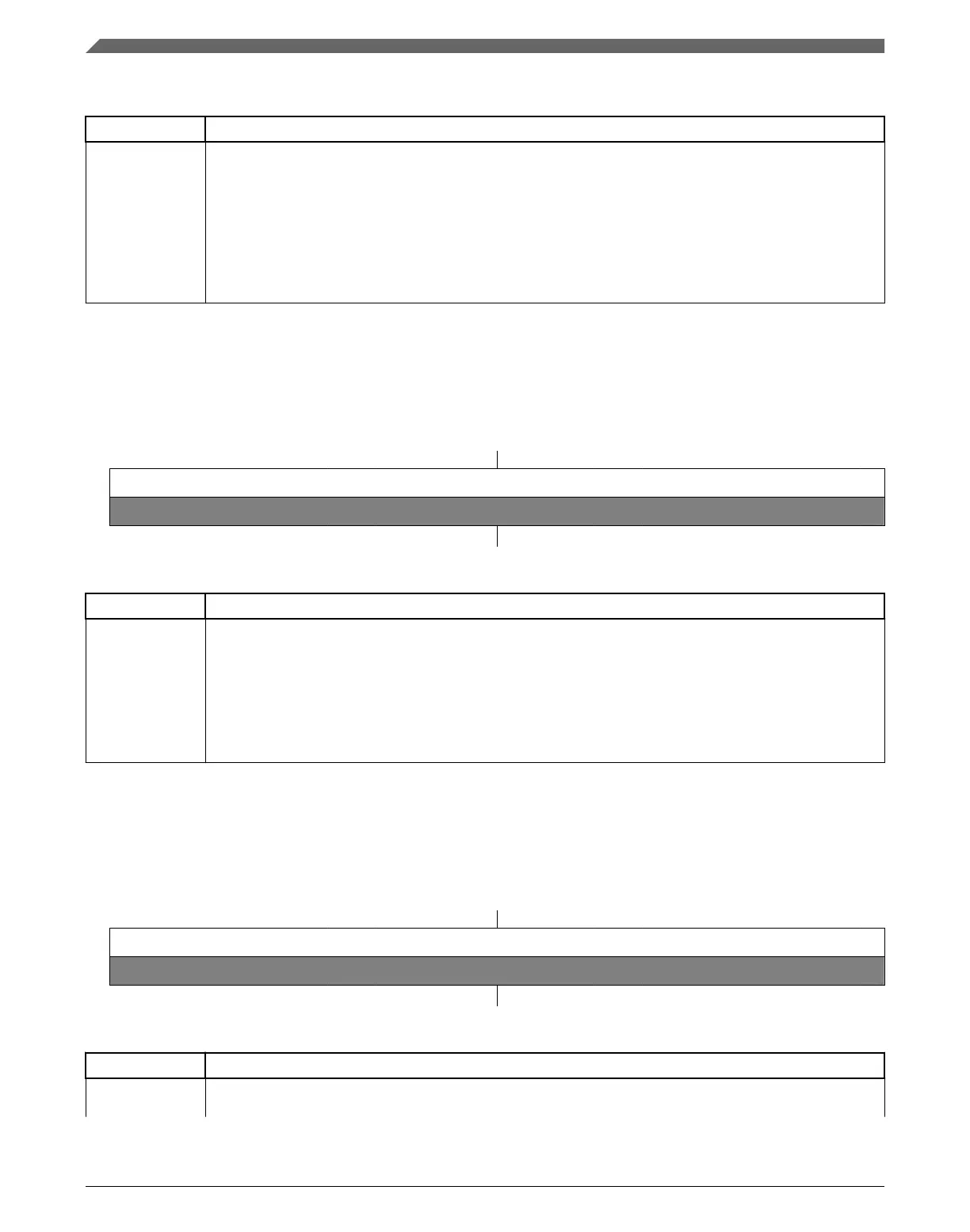

3.3.39 Tx Buffer Transmission Occurred Register (M_CAN_TXBTO)

Address: 0h base + D8h offset = D8h

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

TO

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

M_CAN_TXBTO field descriptions

Field Description

0–31

TO

Transmission Occurred

Each Tx Buffer has its own Transmission Occurred bit. The bits are set when the corresponding TXBRP

bit is cleared after a successful transmission. The bits are reset when a new transmission is requested by

writing 1 to the corresponding bit of register TXBAR.

0 No transmission occurred

1 Transmission occurred

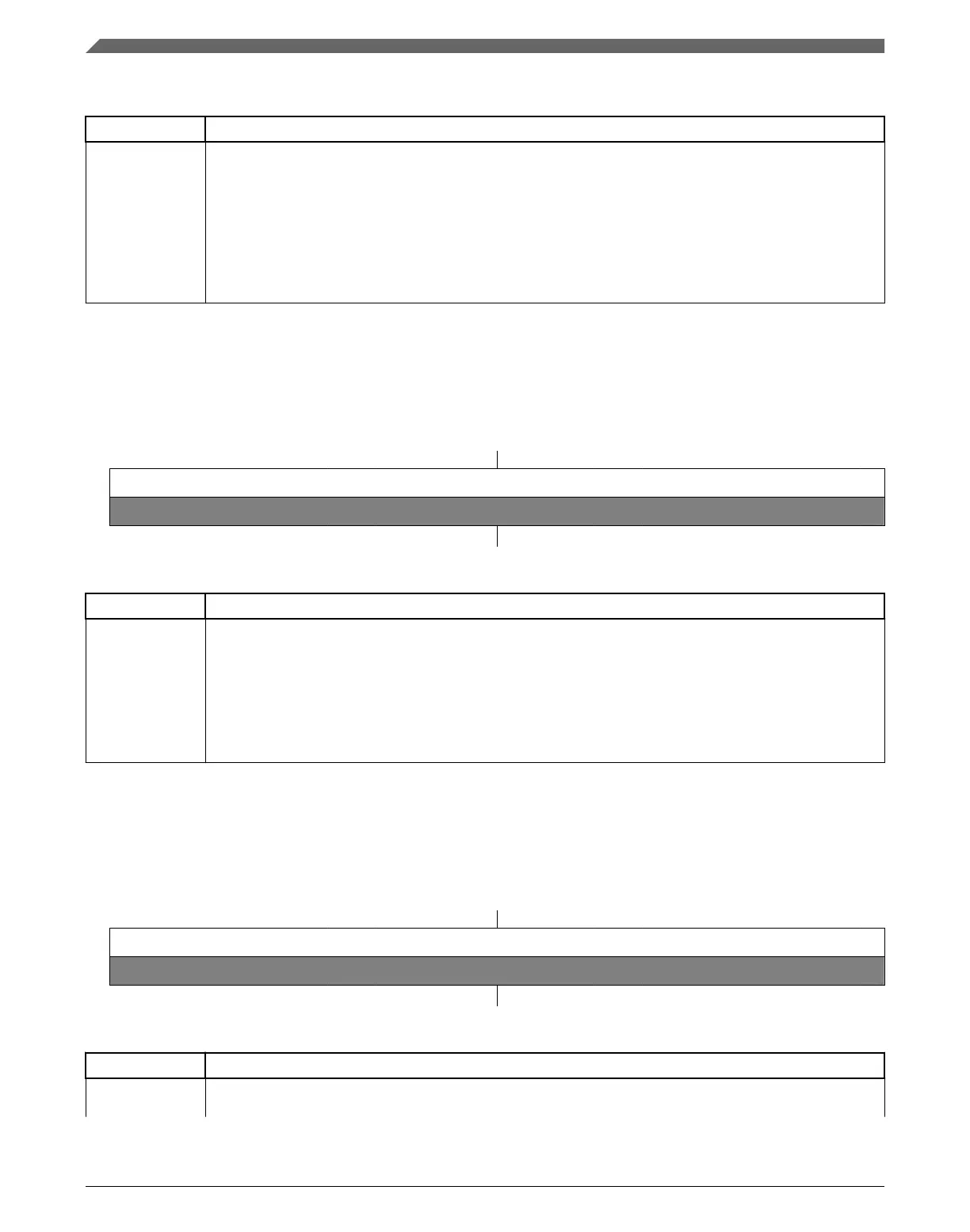

3.3.40 Tx Buffer Cancellation Finished Register (M_CAN_TXBCF)

Address: 0h base + DCh offset = DCh

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

CF

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

M_CAN_TXBCF field descriptions

Field Description

0–31

CF

Cancellation Finished

Memory Map and Register Description

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

74 Freescale Semiconductor, Inc.

Loading...

Loading...