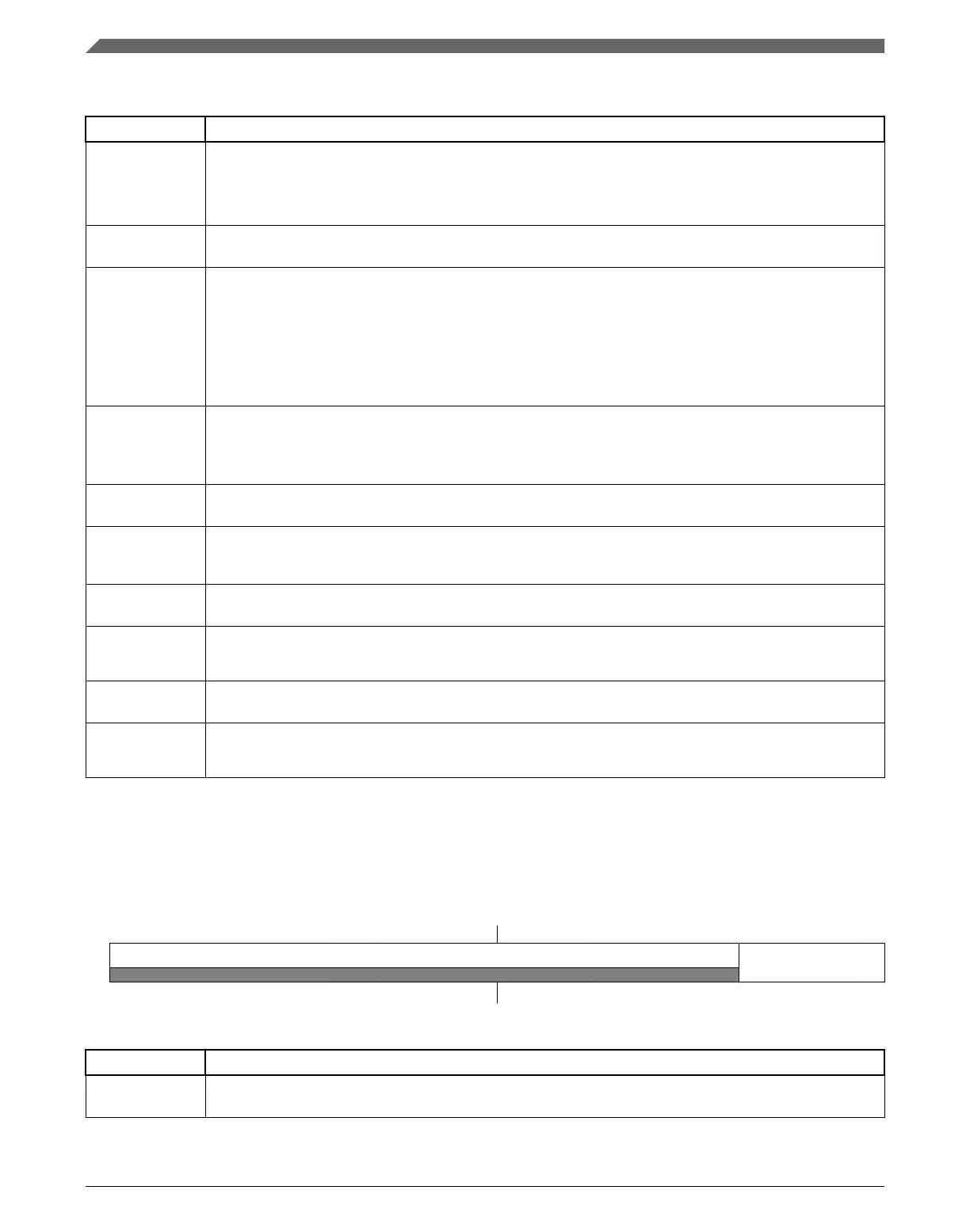

M_CAN_RXF1S field descriptions (continued)

Field Description

00 Idle state, wait for reception of debug messages, DMA request is cleared

01 Debug message A received

10 Debug messages A, B received

11 Debug messages A, B, C received, DMA request is set

2–5

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

6

RF1L

Rx FIFO 1 Message Lost

This bit is a copy of interrupt flag IR[RF1L]. When IR[RF1L] is reset, this bit is also reset.

NOTE: Overwriting the oldest message when RXF1C[F1OM] = 1 will not set this flag.

0 No Rx FIFO 1 message lost

1 Rx FIFO 1 message lost, also set after write attempt to Rx FIFO 1 of size zero

7

F1F

Rx FIFO 1 Full

0 Rx FIFO 1 not full

1 Rx FIFO 1 full

8–9

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

10–15

F1PI

Rx FIFO 1 Put Index

Rx FIFO 1 write index pointer, range 0 to 63.

16–17

Reserved

This field is reserved.

18–23

F1GI

Rx FIFO 1 Get Index

Rx FIFO 1 read index pointer, range 0 to 63.

24

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

25–31

F1FL

Rx FIFO 1 Fill Level

Number of elements stored in Rx FIFO 1, range 0 to 64.

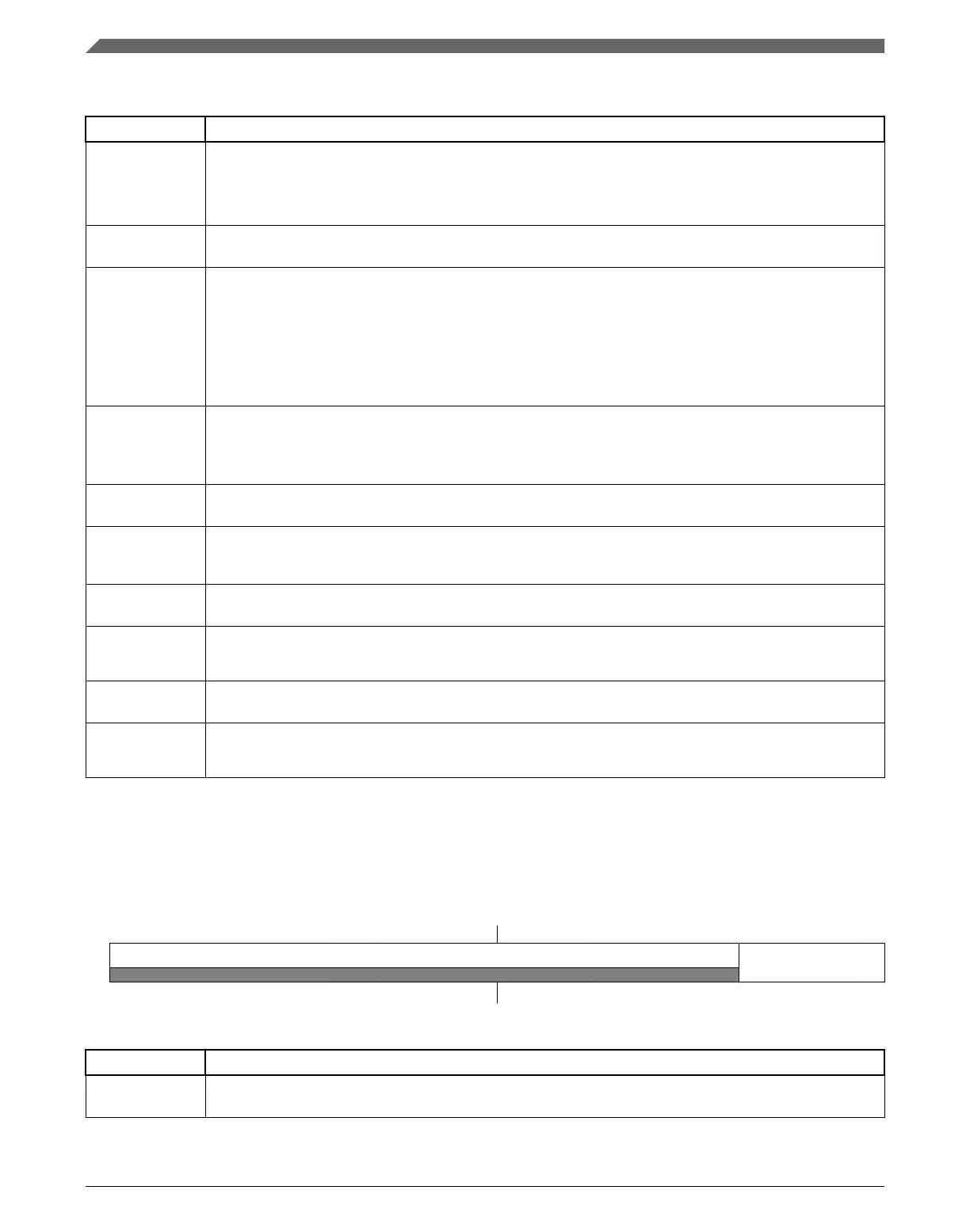

3.3.31 Rx FIFO 1 Acknowledge Register (M_CAN_RXF1A)

Address: 0h base + B8h offset = B8h

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

0

F1AI

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

M_CAN_RXF1A field descriptions

Field Description

0–25

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

Table continues on the next page...

Memory Map and Register Description

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

66 Freescale Semiconductor, Inc.

Loading...

Loading...