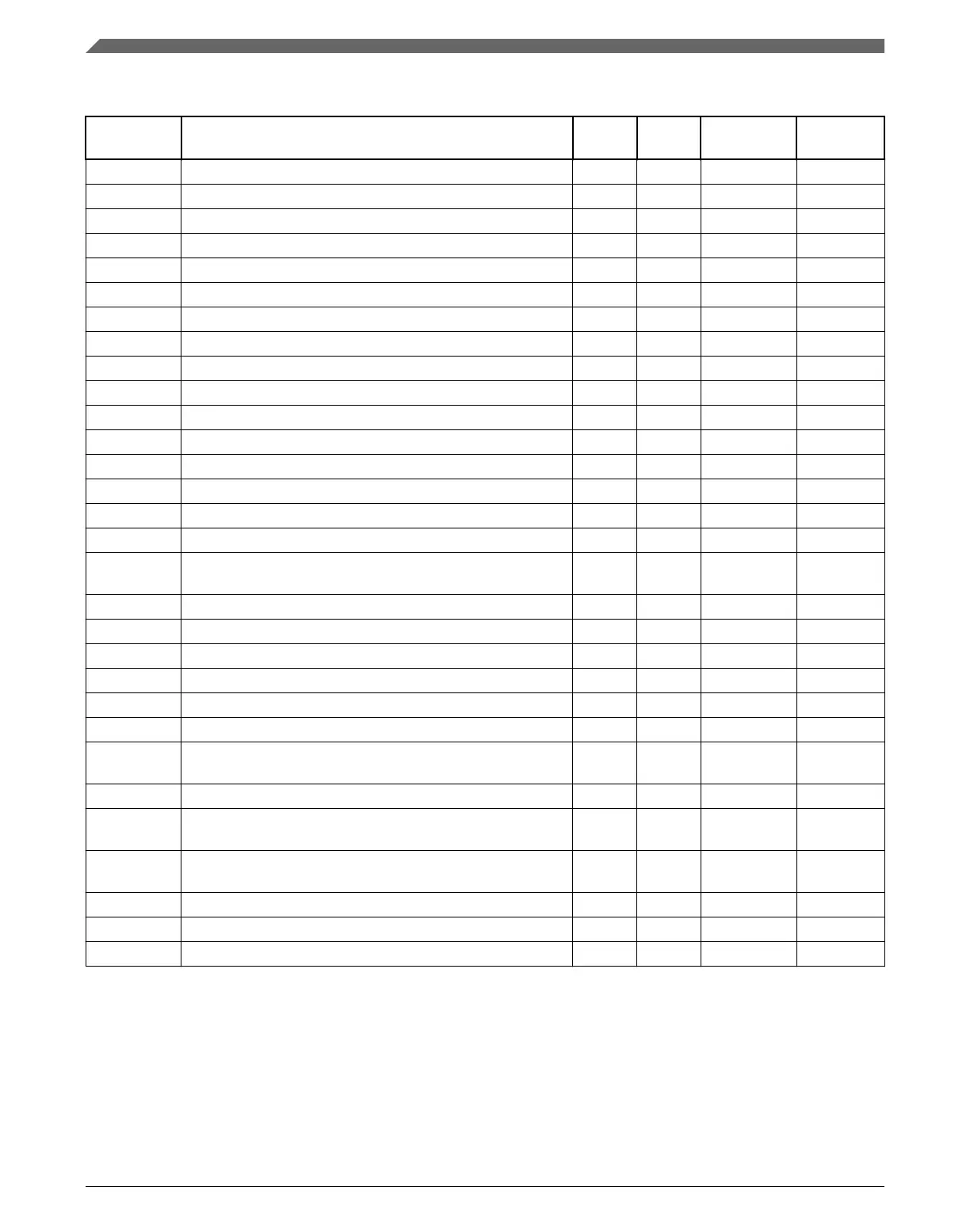

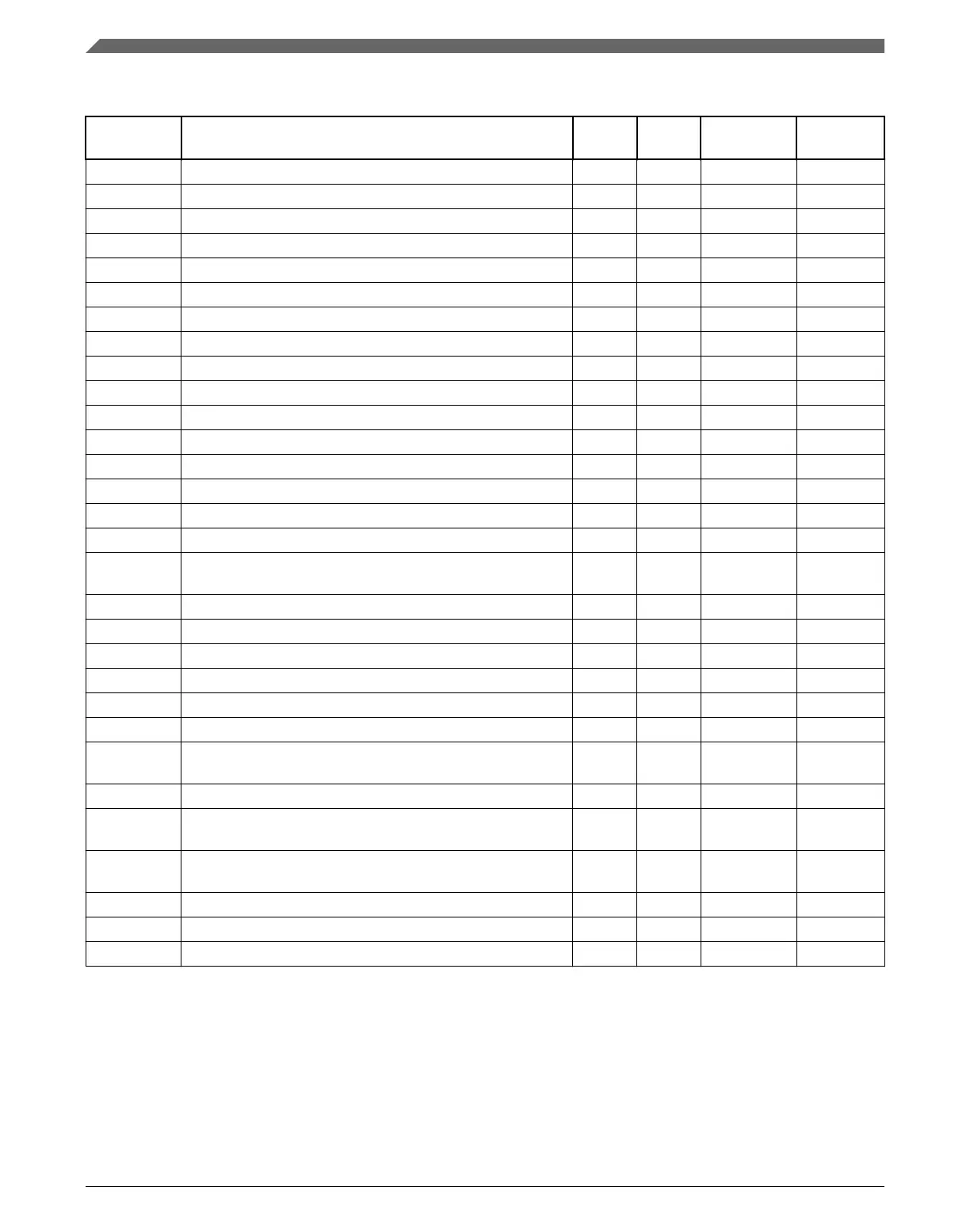

M_CAN memory map (continued)

Address

offset (hex)

Register name

Width

(in bits)

Access Reset value

Section/

page

58 Interrupt Line Select Register (M_CAN_ILS) 32 R/W 0000_0000h 3.3.16/52

5C Interrupt Line Enable Register (M_CAN_ILE) 32 R/W 0000_0000h 3.3.17/55

80 Global Filter Configuration Register (M_CAN_GFC) 32 R/W 0000_0000h 3.3.18/56

84 Standard ID Filter Configuration Register (M_CAN_SIDFC) 32 R/W 0000_0000h 3.3.19/57

88 Extended ID Filter Configuration Register (M_CAN_XIDFC) 32 R/W 0000_0000h 3.3.20/58

90 Extended ID and Mask Register (M_CAN_XIDAM) 32 R/W 1FFF_FFFFh 3.3.21/59

94 High Priority Message Status Register (M_CAN_HPMS) 32 R 0000_0000h 3.3.22/59

98 New Data 1 Register (M_CAN_NDAT1) 32 R/W 0000_0000h 3.3.23/60

9C New Data 2 Register (M_CAN_NDAT2) 32 R/W 0000_0000h 3.3.24/61

A0 Rx FIFO 0 Configuration Register (M_CAN_RXF0C) 32 R/W 0000_0000h 3.3.25/61

A4 Rx FIFO 0 Status Register (M_CAN_RXF0S) 32 R 0000_0000h 3.3.26/62

A8 Rx FIFO 0 Acknowledge Register (M_CAN_RXF0A) 32 R/W 0000_0000h 3.3.27/63

AC Rx Buffer Configuration Register (M_CAN_RXBC) 32 R/W 0000_0000h 3.3.28/64

B0 Rx FIFO 1 Configuration Register (M_CAN_RXF1C) 32 R/W 0000_0000h 3.3.29/64

B4 Rx FIFO 1 Status Register (M_CAN_RXF1S) 32 R 0000_0000h 3.3.30/65

B8 Rx FIFO 1 Acknowledge Register (M_CAN_RXF1A) 32 R/W 0000_0000h 3.3.31/66

BC

Rx Buffer / FIFO Element Size Configuration Register

(M_CAN_RXESC)

32 R/W 0000_0000h 3.3.32/67

C0 Tx Buffer Configuration Register (M_CAN_TXBC) 32 R/W 0000_0000h 3.3.33/69

C4 Tx FIFO/Queue Status Register (M_CAN_TXFQS) 32 R 0000_0000h 3.3.34/70

C8 Tx Buffer Element Size Configuration (M_CAN_TXESC) 32 R/W 0000_0000h 3.3.35/71

CC Tx Buffer Request Pending Register (M_CAN_TXBRP) 32 R 0000_0000h 3.3.36/72

D0 Tx Buffer Add Request Register (M_CAN_TXBAR) 32 R/W 0000_0000h 3.3.37/73

D4 Tx Buffer Cancellation Request Register (M_CAN_TXBCR) 32 R/W 0000_0000h 3.3.38/73

D8

Tx Buffer Transmission Occurred Register

(M_CAN_TXBTO)

32 R 0000_0000h 3.3.39/74

DC Tx Buffer Cancellation Finished Register (M_CAN_TXBCF) 32 R 0000_0000h 3.3.40/74

E0

Tx Buffer Transmission Interrupt Enable Register

(M_CAN_TXBTIE)

32 R/W 0000_0000h 3.3.41/75

E4

Tx Buffer Cancellation Finished Interrupt Enable Register

(M_CAN_TXBCIE)

32 R/W 0000_0000h 3.3.42/75

F0 Tx Event FIFO Configuration Register (M_CAN_TXEFC) 32 R/W 0000_0000h 3.3.43/76

F4 Tx Event FIFO Status Register (M_CAN_TXEFS) 32 R 0000_0000h 3.3.44/77

F8 Tx Event FIFO Acknowledge Register (M_CAN_TXEFA) 32 R/W 0000_0000h 3.3.45/78

3.3.1 Core Release Register (M_CAN_CREL)

The following table shows example field values for this register and explains how they

encode a particular M_CAN core release.

Memory Map and Register Description

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

28 Freescale Semiconductor, Inc.

Loading...

Loading...