3.3.15 Interrupt Enable Register (M_CAN_IE)

The settings in the Interrupt Enable register determine which status changes in the

Interrupt Register will be signaled on an interrupt line.

Address: 0h base + 54h offset = 54h

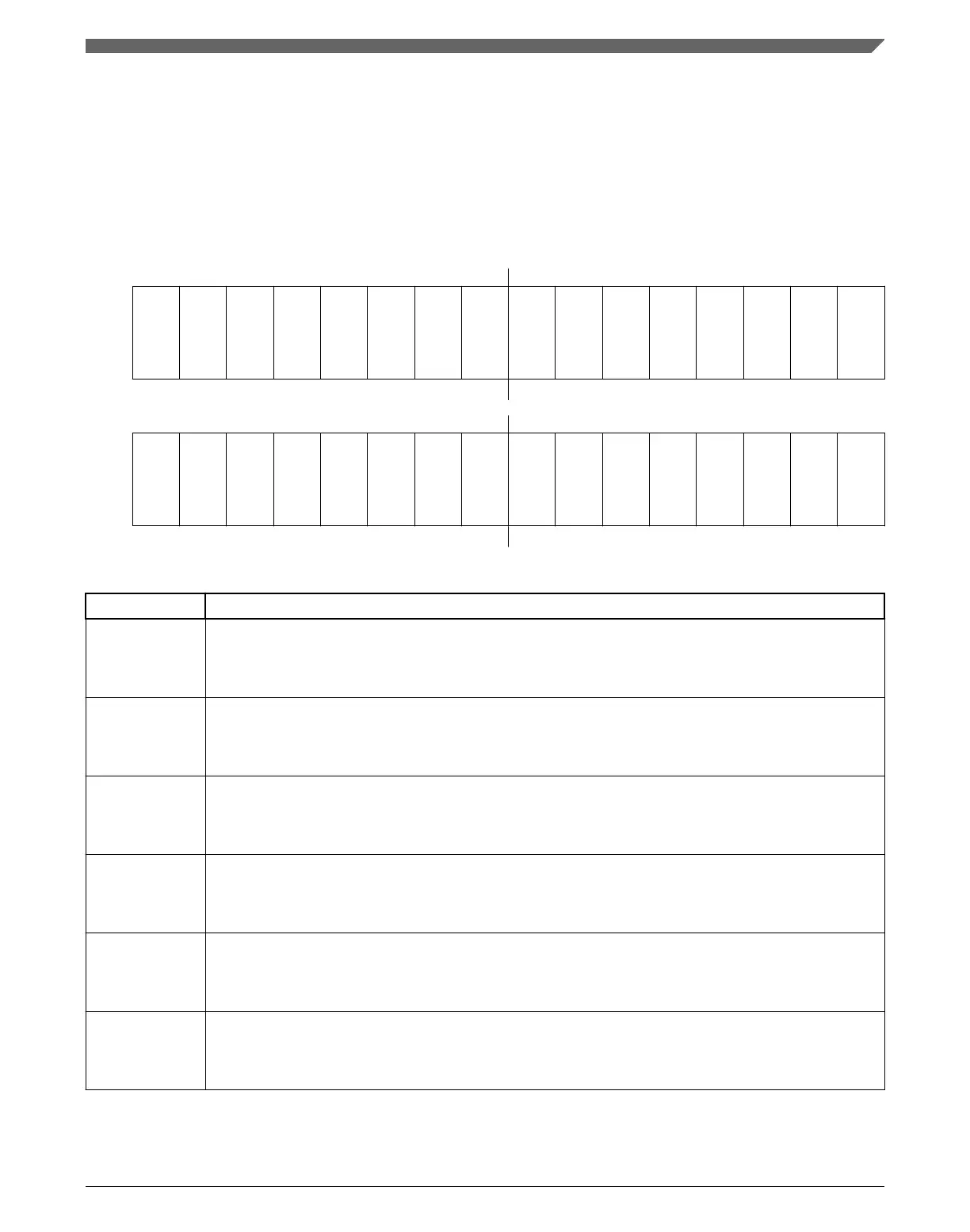

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R

STEE FOEE

ACKEE

BEE

CRCEE

WDIE BOE EWE EPE ELOE BEUE BECE DRXE

TOOE

MRAFE

TSWE

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

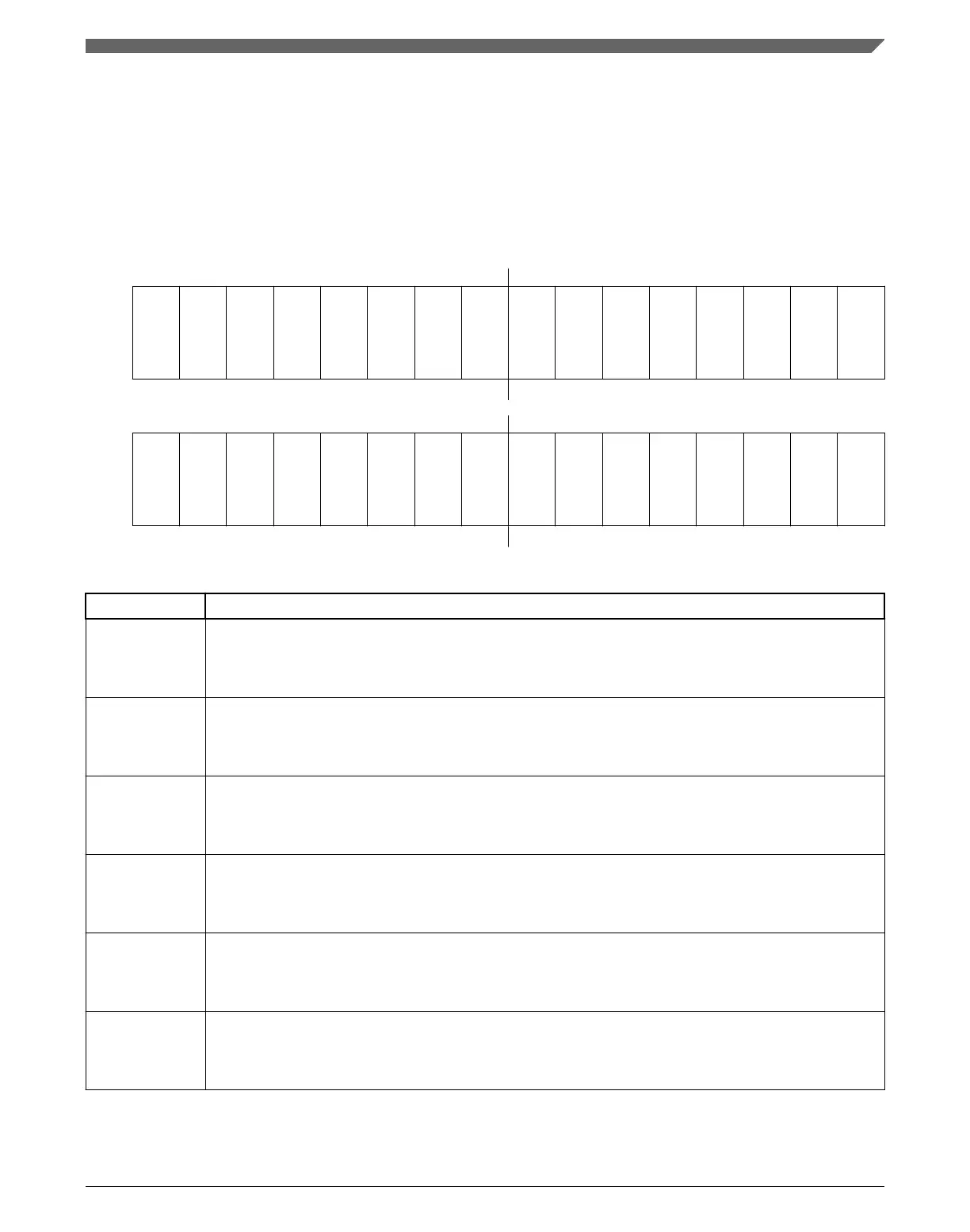

Bit

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

TEFLE

TEFFE

TEFWE

TEFNE

TFEE TCFE TCE

HPME

RF1LE

RF1FE

RF1WE

RF1NE

RF0LE

RF0FE

RF0WE

RF0NE

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

M_CAN_IE field descriptions

Field Description

0

STEE

Stuff Error Interrupt Enable

0 Interrupt disabled

1 Interrupt enabled

1

FOEE

Format Error Interrupt Enable

0 Interrupt disabled

1 Interrupt enabled

2

ACKEE

Acknowledge Error Interrupt Enable

0 Interrupt disabled

1 Interrupt enabled

3

BEE

Bit Error Interrupt Enable

0 Interrupt disabled

1 Interrupt enabled

4

CRCEE

CRC Error Interrupt Enable

0 Interrupt disabled

1 Interrupt enabled

5

WDIE

Watchdog Interrupt Enable

0 Interrupt disabled

1 Interrupt enabled

Table continues on the next page...

Chapter 3 Modular CAN (M_CAN)

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 49

Loading...

Loading...