M_CAN_RWD field descriptions (continued)

Field Description

16–23

WDV

Watchdog Value

Actual Message RAM Watchdog Counter Value.

24–31

WDC

Watchdog Configuration

Start value of the Message RAM Watchdog Counter. With the reset value of 00 the counter is disabled.

NOTE: This field has Protected Write status.

3.3.6 CC Control Register (M_CAN_CCCR)

For details about setting and resetting of single bits see Software Initialization.

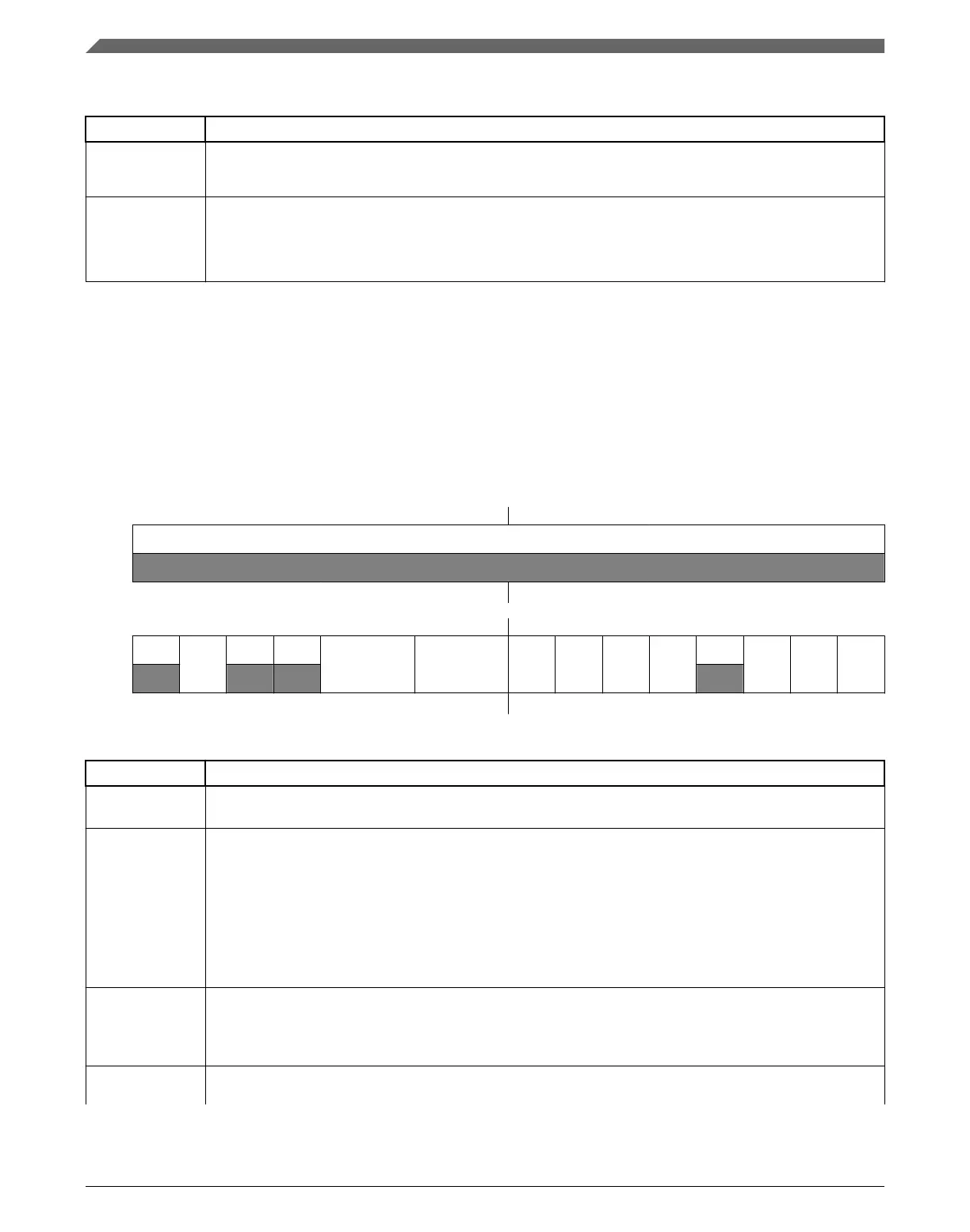

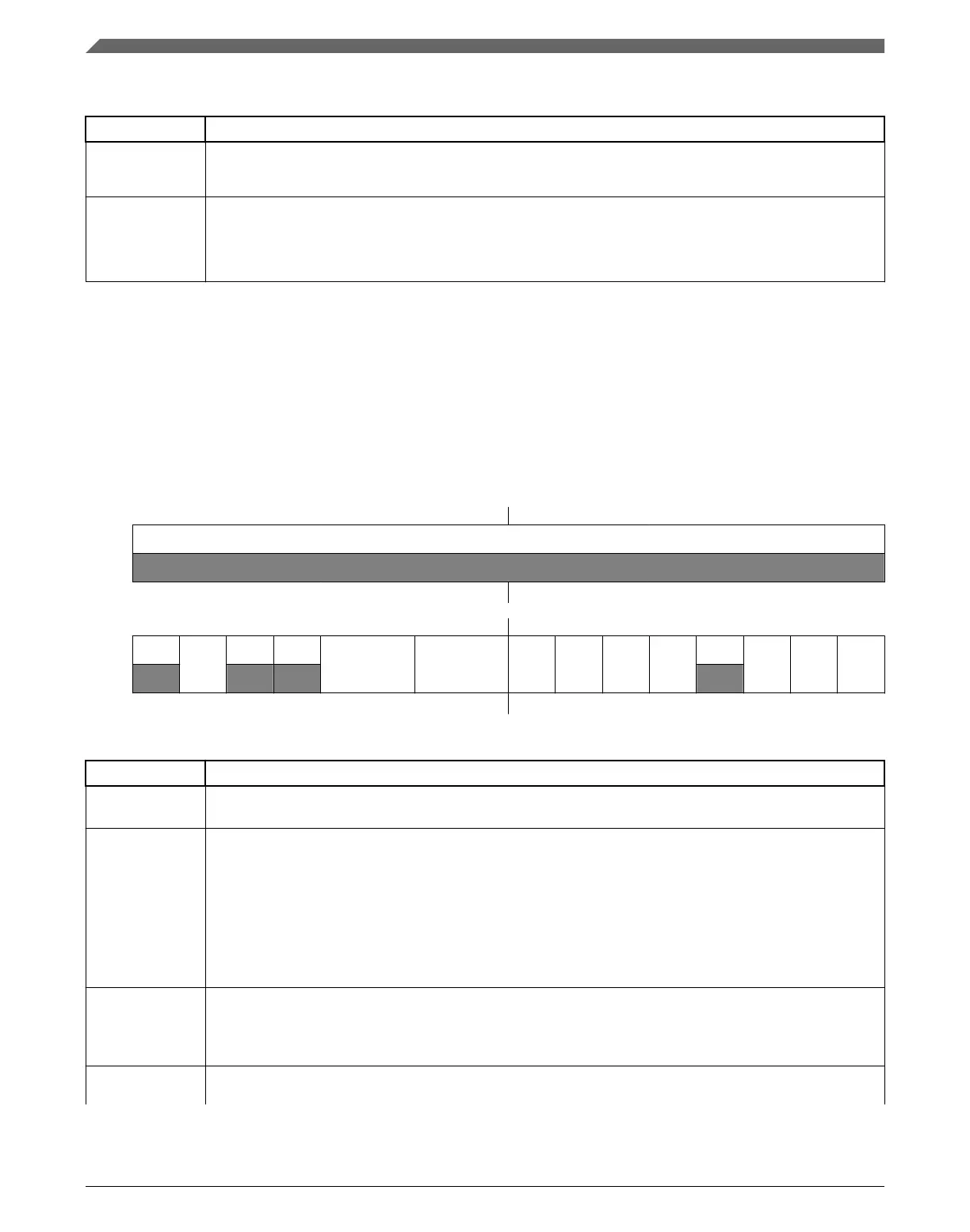

Address: 0h base + 18h offset = 18h

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R

0

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bit

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

0

TXP

FDBS FDO

CMR CME TEST DAR MON CSR

CSA

ASM CCE INIT

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1

M_CAN_CCCR field descriptions

Field Description

0–16

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

17

TXP

Transmit Pause

If this bit is set, the M_CAN pauses for two CAN bit times before starting the next transmission after itself

has successfully transmitted a frame (see Tx Handling).

NOTE: This field has Protected Write status.

0 Transmit pause disabled

1 Transmit pause enabled

18

FDBS

CAN FD Bit Rate Switching

0 This node transmits no frames with bit rate switching

1 This node transmits all frames (excluding remote frames) with bit rate switching

19

FDO

CAN FD Operation

Table continues on the next page...

Memory Map and Register Description

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

34 Freescale Semiconductor, Inc.

Loading...

Loading...