M_CAN_TXBC field descriptions (continued)

Field Description

10–15

NDTB

Number of Dedicated Transmit Buffers

NOTE: This field has Protected Write status.

0 No Dedicated Tx Buffers

1-32 Number of Dedicated Tx Buffers

>32 Values greater than 32 are interpreted as 32

16–29

TBSA

Tx Buffers Start Address

Start address of Tx Buffers section in Message RAM (32-bit word address, see Message RAM ).

NOTE: This field has Protected Write status.

30–31

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

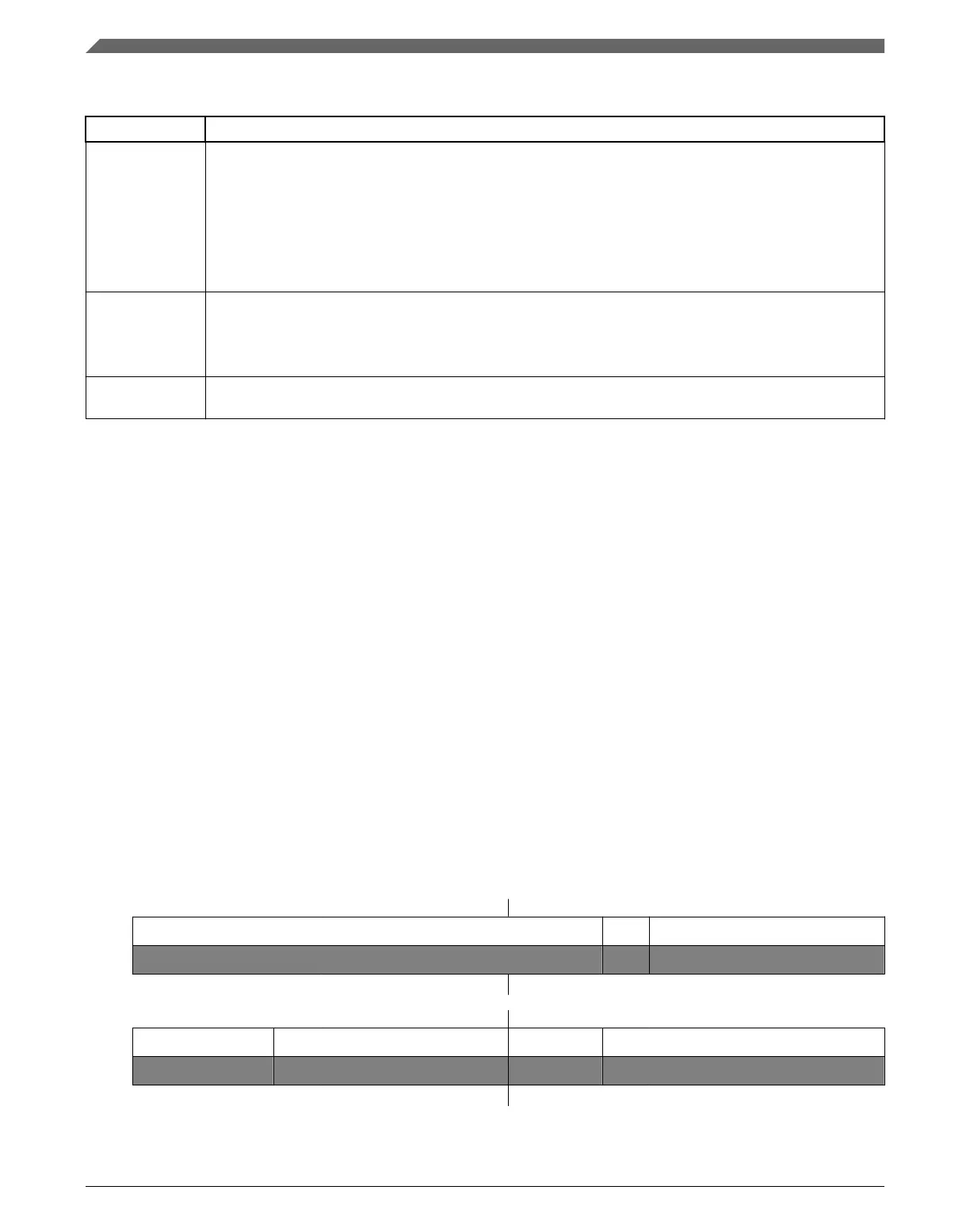

3.3.34 Tx FIFO/Queue Status Register (M_CAN_TXFQS)

The Tx FIFO/Queue status is related to the pending Tx requests listed in register TXBRP.

Therefore the effect of Add/Cancellation requests may be delayed due to a running Tx

scan (TXBRP not yet updated).

NOTE

In case of mixed configurations where dedicated Tx Buffers are

combined with a Tx FIFO or a Tx Queue, the Put and Get

Indices indicate the number of the Tx Buffer starting with the

first dedicated Tx Buffers.

Example: For a configuration of 12 dedicated Tx Buffers and a

Tx FIFO of 20 Buffers a Put Index of 15 points to the fourth

buffer of the Tx FIFO.

Address: 0h base + C4h offset = C4h

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R

0 TFQF TFQPI

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bit

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

0 TFGI 0 TFFL

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Memory Map and Register Description

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

70 Freescale Semiconductor, Inc.

Loading...

Loading...