M_CAN_TOCC field descriptions (continued)

Field Description

When operating in Continuous mode, a write to TOCV presets the counter to the value configured by

TOCC[TOP] and continues down-counting. When the Timeout Counter is controlled by one of the FIFOs,

an empty FIFO presets the counter to the value configured by TOCC[TOP]. Down-counting is started

when the first FIFO element is stored.

NOTE: This field has Protected Write status.

00 Continuous operation

01 Timeout controlled by Tx Event FIFO

10 Timeout controlled by Rx FIFO 0

11 Timeout controlled by Rx FIFO 1

31

ETOC

Enable Timeout Counte

NOTE: This field has Protected Write status.

0 Timeout Counter disabled

1 Timeout Counter enabled

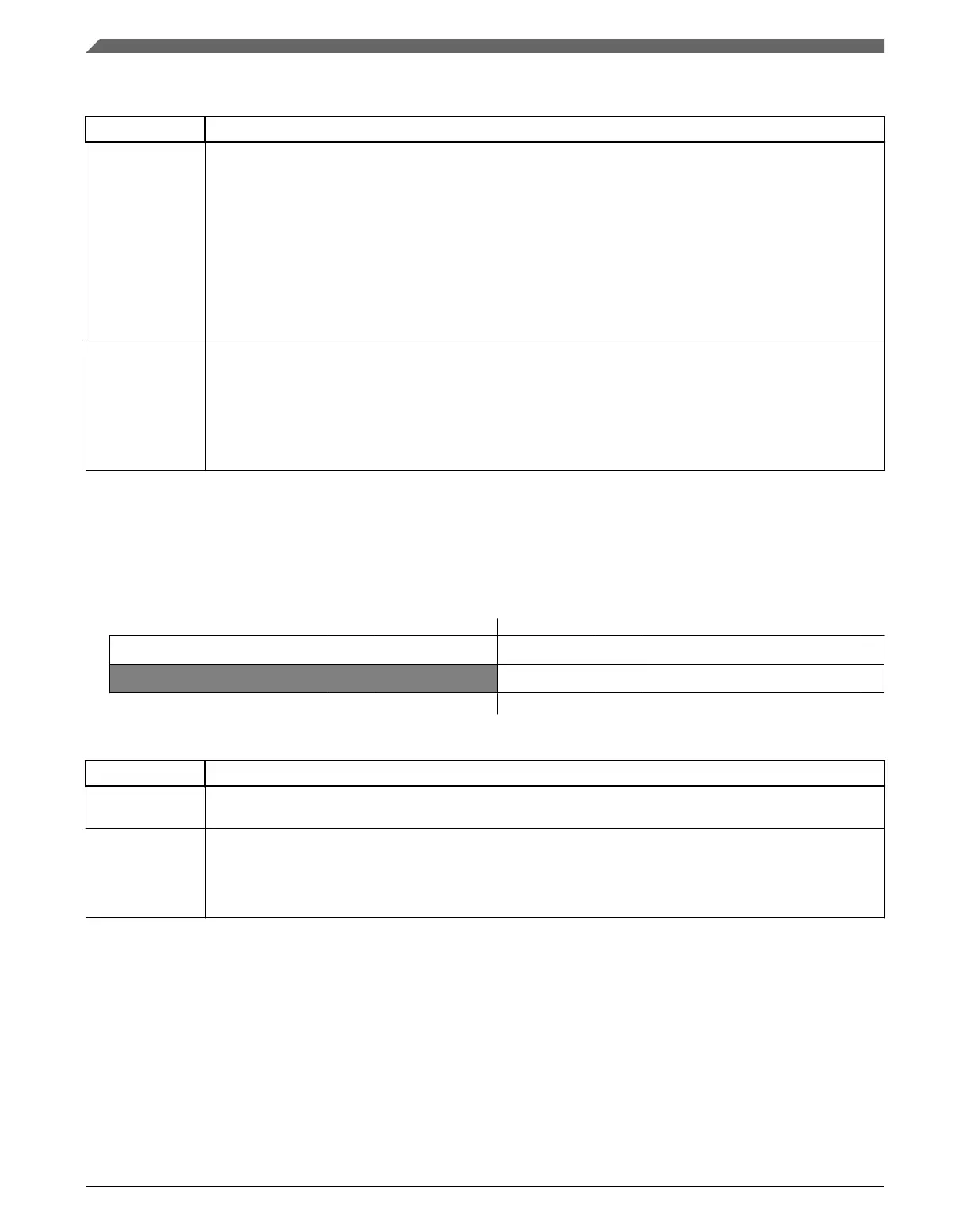

3.3.11 Timeout Counter Value Register (M_CAN_TOCV)

Address: 0h base + 2Ch offset = 2Ch

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

0 TOC

W

w1c

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

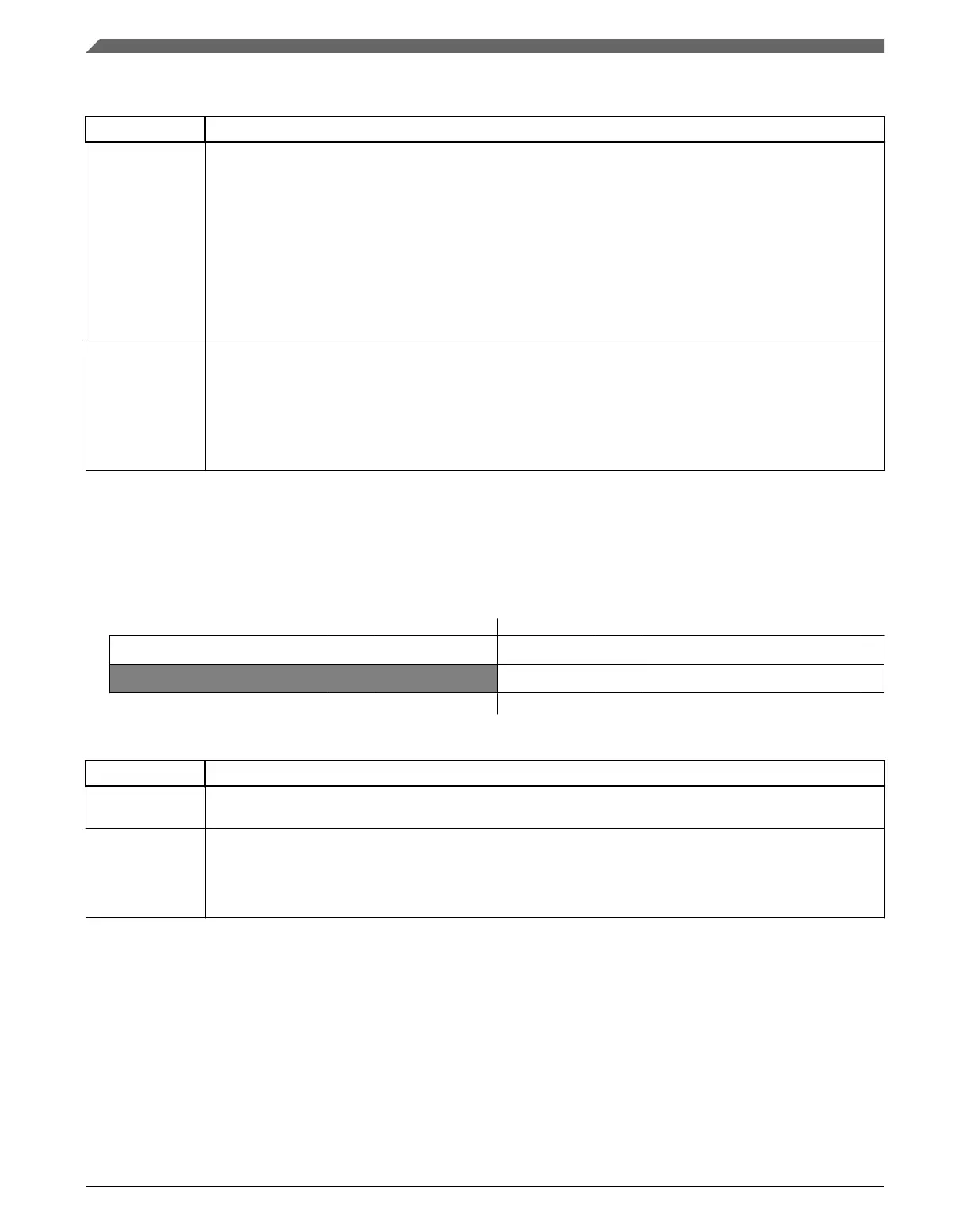

M_CAN_TOCV field descriptions

Field Description

0–15

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

16–31

TOC

Timeout Counter

The Timeout Counter is decremented in multiples of CAN bit times [1…16] depending on the configuration

of TSCC[TCP]. When decremented to zero, interrupt flag IR[TOO] is set and the Timeout Counter is

stopped. Start and reset/restart conditions are configured via TOCC[TOS].

Memory Map and Register Description

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

40 Freescale Semiconductor, Inc.

Loading...

Loading...