3.3.13 Protocol Status Register (M_CAN_PSR)

NOTE

When a frame in CAN FD format has reached the data phase

with BRS flag set, the next CAN event (error or valid frame)

will be shown in FLEC instead of LEC. An error in a fixed stuff

bit of a CAN FD CRC sequence will be shown as a Form Error,

not Stuff Error.

NOTE

The Bus_Off recovery sequence (see CAN Specification Rev.

2.0 or ISO11898-1) cannot be shortened by setting or resetting

CCCR[INIT]. If the device goes Bus_Off, it will set

CCCR[INIT] of its own accord, stopping all bus activities.

Once CCCR[INIT] has been cleared by the CPU, the device

will then wait for 129 occurrences of Bus Idle (129 x 11

consecutive recessive bits) before resuming normal operation.

At the end of the Bus_Off recovery sequence, the Error

Management Counters will be reset. During the waiting time

after the resetting of CCCR[INIT], each time a sequence of 11

recessive bits has been monitored, a Bit0Error code is written to

PSR[LEC], enabling the CPU to readily check up whether the

CAN bus is stuck at dominant or continuously disturbed and to

monitor the Bus_Off recovery sequence. ECR[REC] is used to

count these sequences.

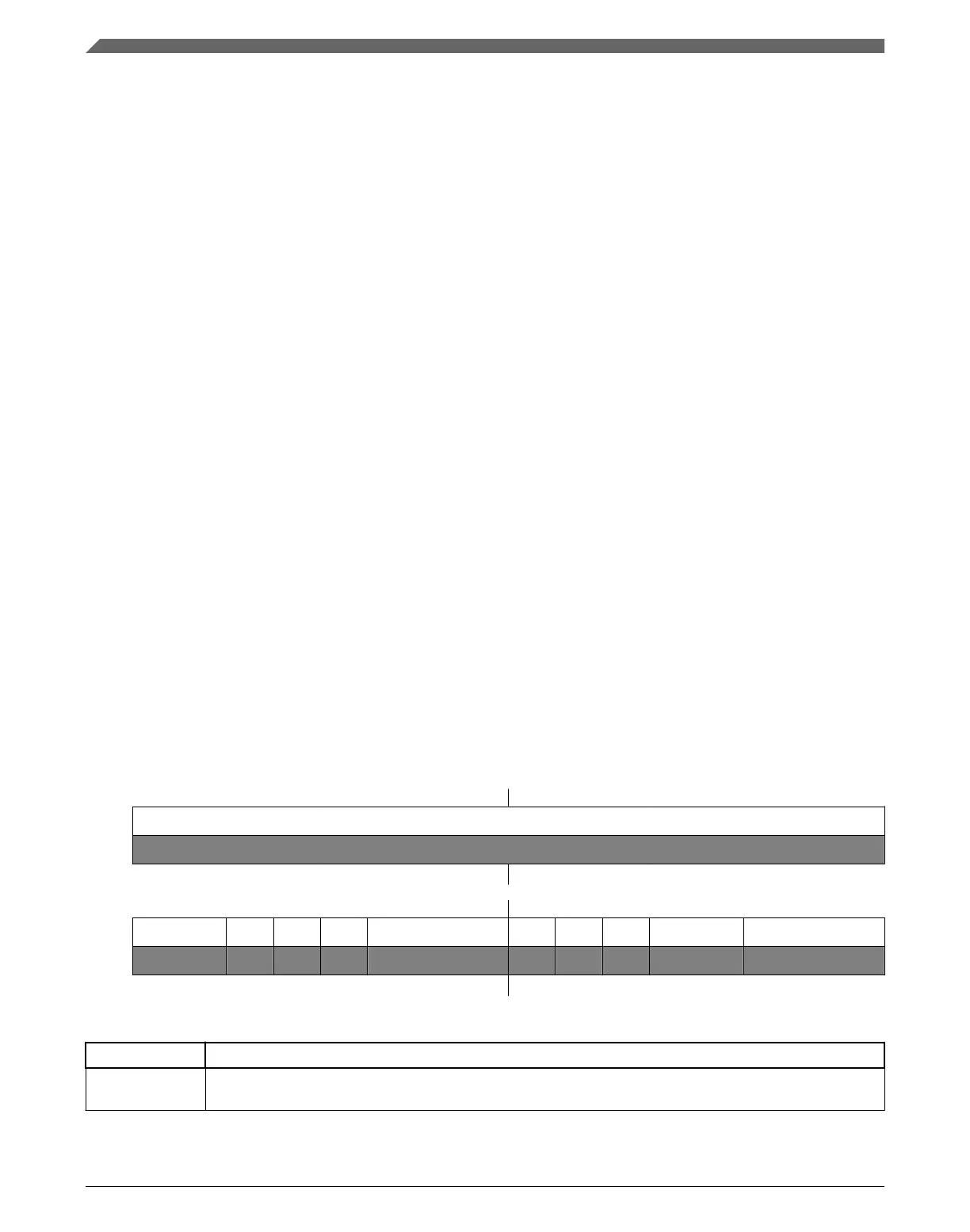

Address: 0h base + 44h offset = 44h

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R

0

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bit

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

0 REDL RBRS RESI FLEC BO EW EP ACT LEC

W

Reset

0 0 0 0 0 1 1 1 0 0 0 0 0 1 1 1

M_CAN_PSR field descriptions

Field Description

0–17

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

Table continues on the next page...

Memory Map and Register Description

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

42 Freescale Semiconductor, Inc.

Loading...

Loading...