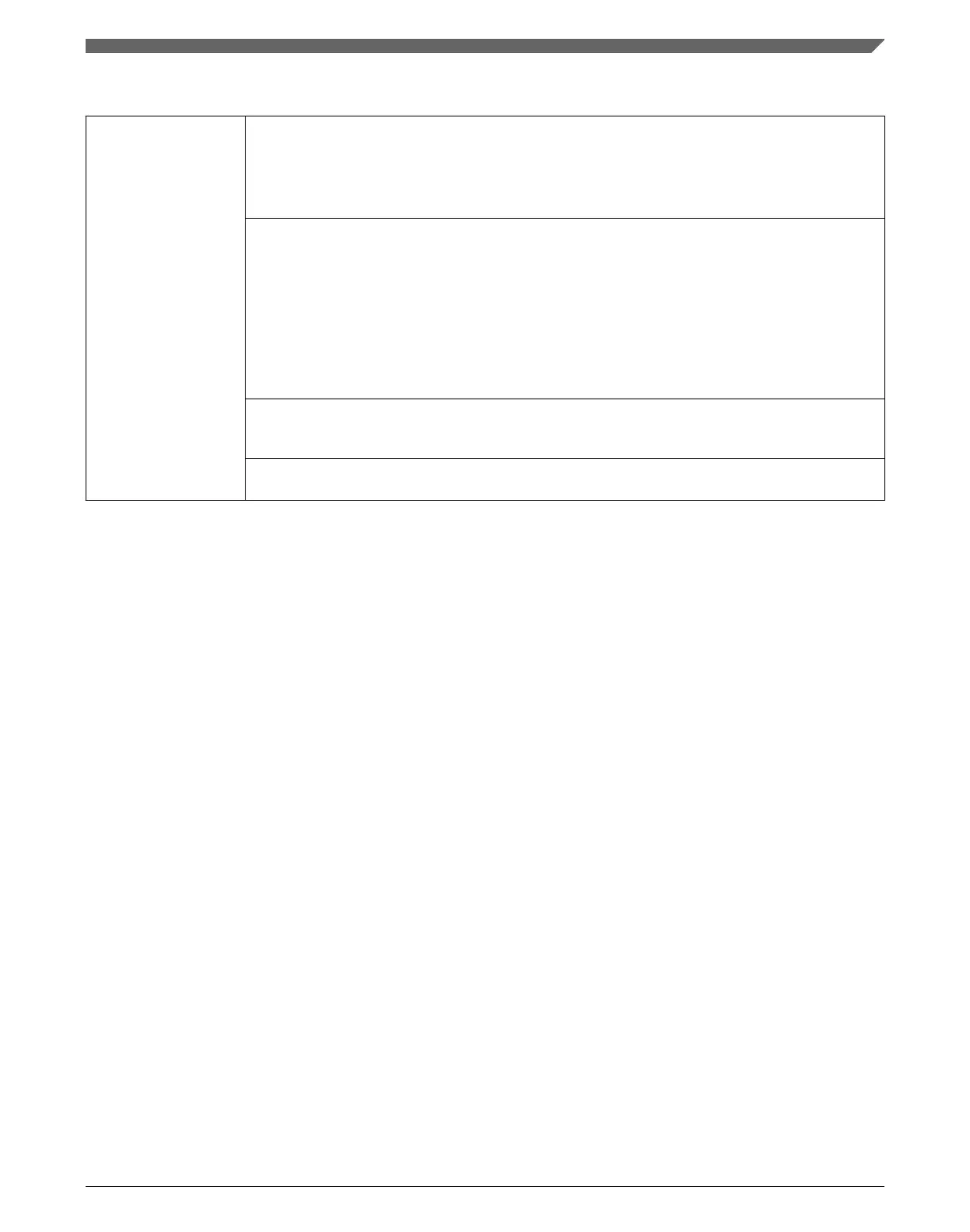

Table 3-57. Extended Message ID Filter Element Field Description (continued)

F1 Bits 28:0 EFID2[28:0]: Extended Filter ID 2

Overall, this bit field has a different meaning depending on the configuration of EFEC:

EFEC = 001...110 Second ID of extended ID filter element

EFEC = 111 Filter for Rx Buffers or for debug messages

EFID2[10:9]: Decides whether the received message is stored into an Rx Buffer or treated as

message A, B, or C of the debug message sequence.

00 Store message into an Rx Buffer

01 Debug Message A

10 Debug Message B

11 Debug Message C

EFID2[8:6]: Is used to control the filter event pins at the Extension Interface. A one at the respective

bit position enables generation of a pulse at the related filter event pin with the duration of one Host

clock period in case the filter matches.

EFID2[5:0]: Defines the offset to the Rx Buffer Start Address RXBC[RBSA] for storage of a

matching message.

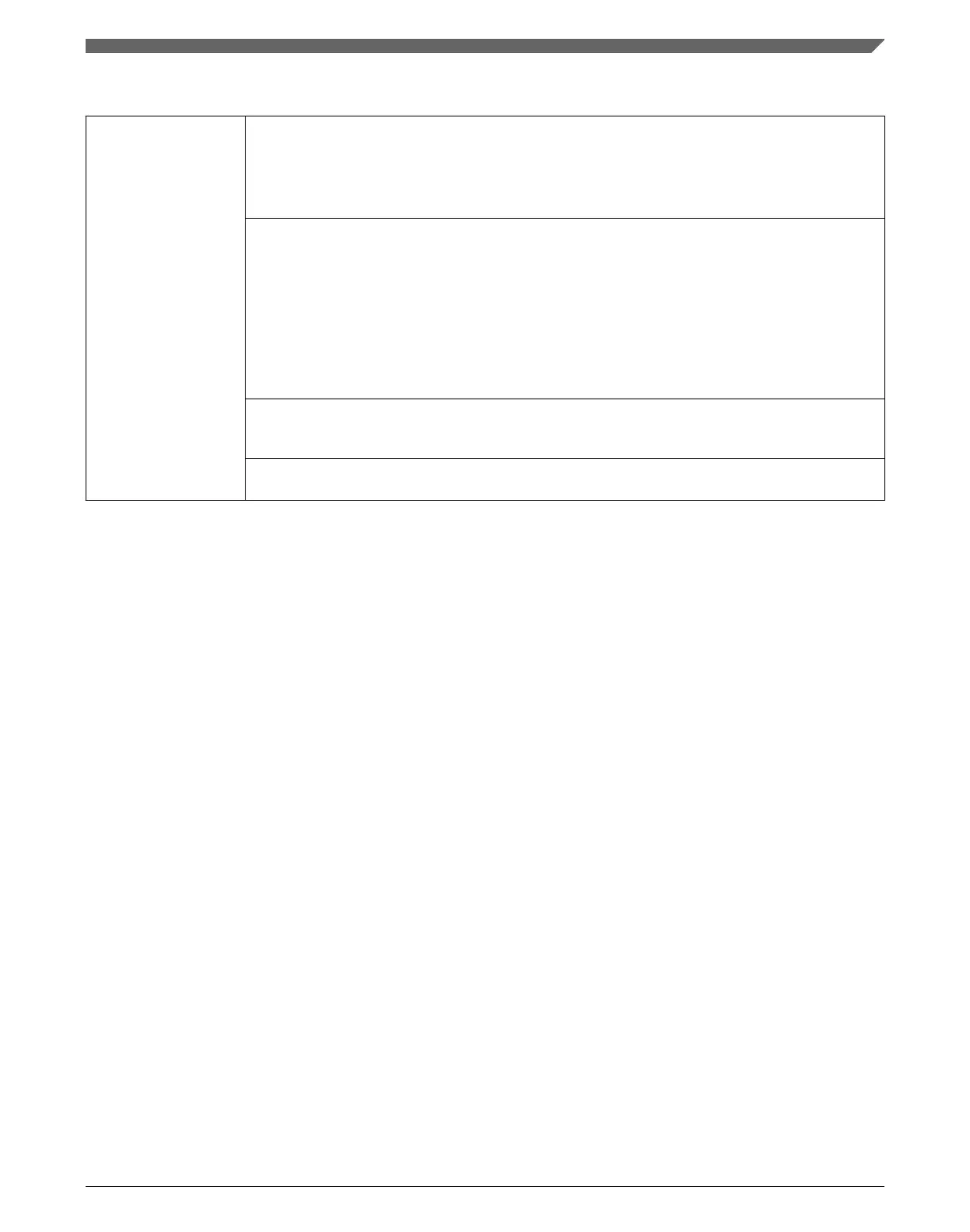

3.5 Functional Description

3.5.1 Operating Modes

3.5.1.1 Software Initialization

Software initialization is started by setting bit CCCR[INIT], either by software or by a

hardware reset, when an uncorrected bit error was detected in the Message RAM, or by

going Bus_Off. While CCCR[INIT] is set, message transfer from and to the CAN bus is

stopped, the status of the CAN bus output M_CAN_Tx is recessive (HIGH). The

counters of the Error Management Logic EML are unchanged. Setting CCCR[INIT] does

not change any configuration register. Resetting CCCR[INIT] finishes the software

initialization. Afterwards the Bit Stream Processor BSP synchronizes itself to the data

transfer on the CAN bus by waiting for the occurrence of a sequence of 11 consecutive

recessive bits (= Bus_Idle) before it can take part in bus activities and start the message

transfer.

Access to the M_CAN configuration registers is only enabled when both bits

CCCR[INIT] and CCCR[CCE] are set (protected write).

Chapter 3 Modular CAN (M_CAN)

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 87

Loading...

Loading...