M_CAN_RXF0C field descriptions (continued)

Field Description

0 FIFO 0 blocking mode

1 FIFO 0 overwrite mode

1–7

F0WM

Rx FIFO 0 Watermark

NOTE: This field has Protected Write status.

0 Watermark interrupt disabled

1-64 Level for Rx FIFO 0 watermark interrupt (IR[RF0W])

>64 Watermark interrupt disabled

8

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

9–15

F0S

Rx FIFO 0 Size

The Rx FIFO 0 elements are indexed from 0 to F0S-1.

NOTE: This field has Protected Write status.

0 No Rx FIFO 0

1-64 Number of Rx FIFO 0 elements

>64 Values greater than 64 are interpreted as 64

16–29

F0SA

Rx FIFO 0 Start Address

Start address of Rx FIFO 0 in Message RAM (32-bit word address, see Message RAM ).

NOTE: This field has Protected Write status.

30–31

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

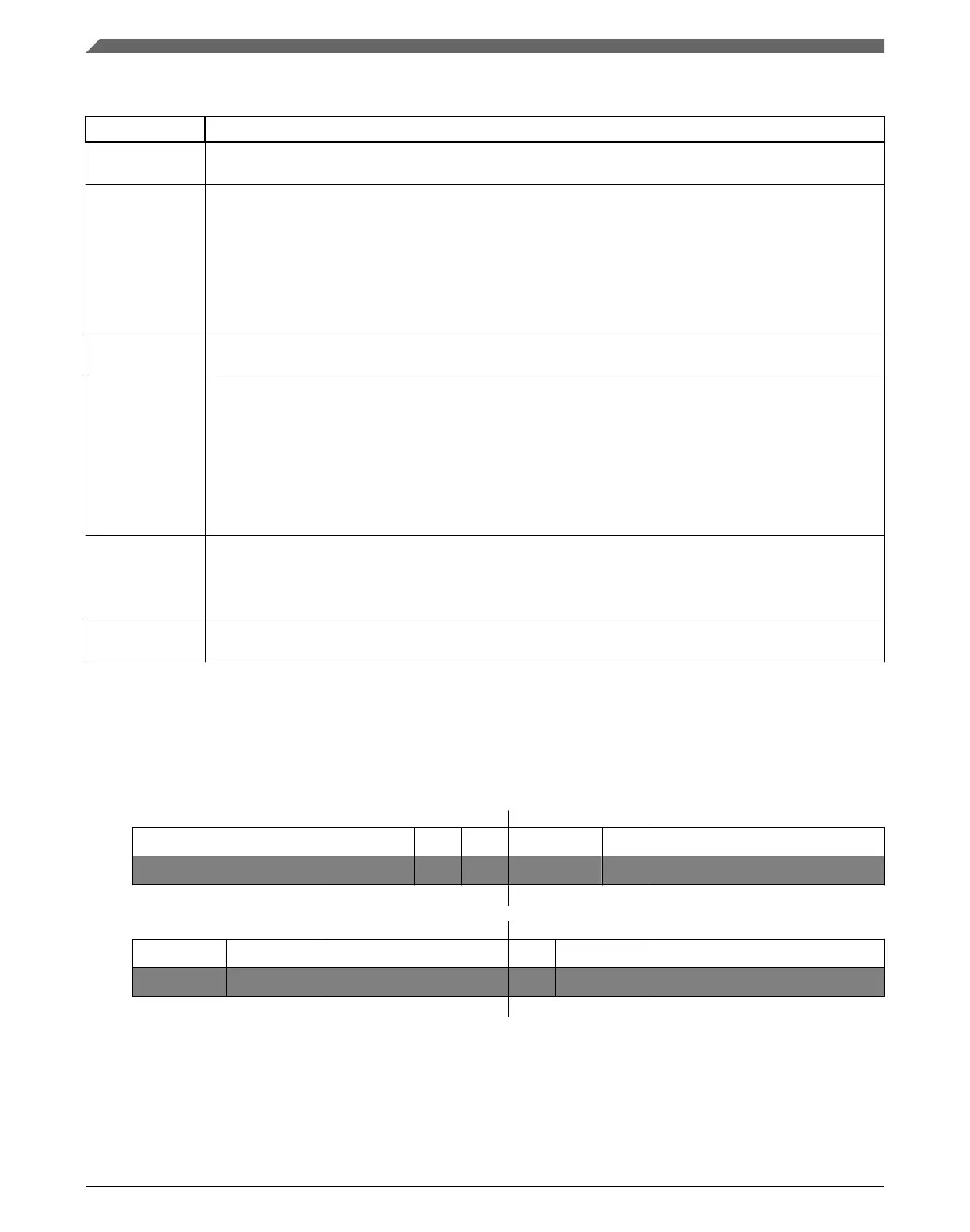

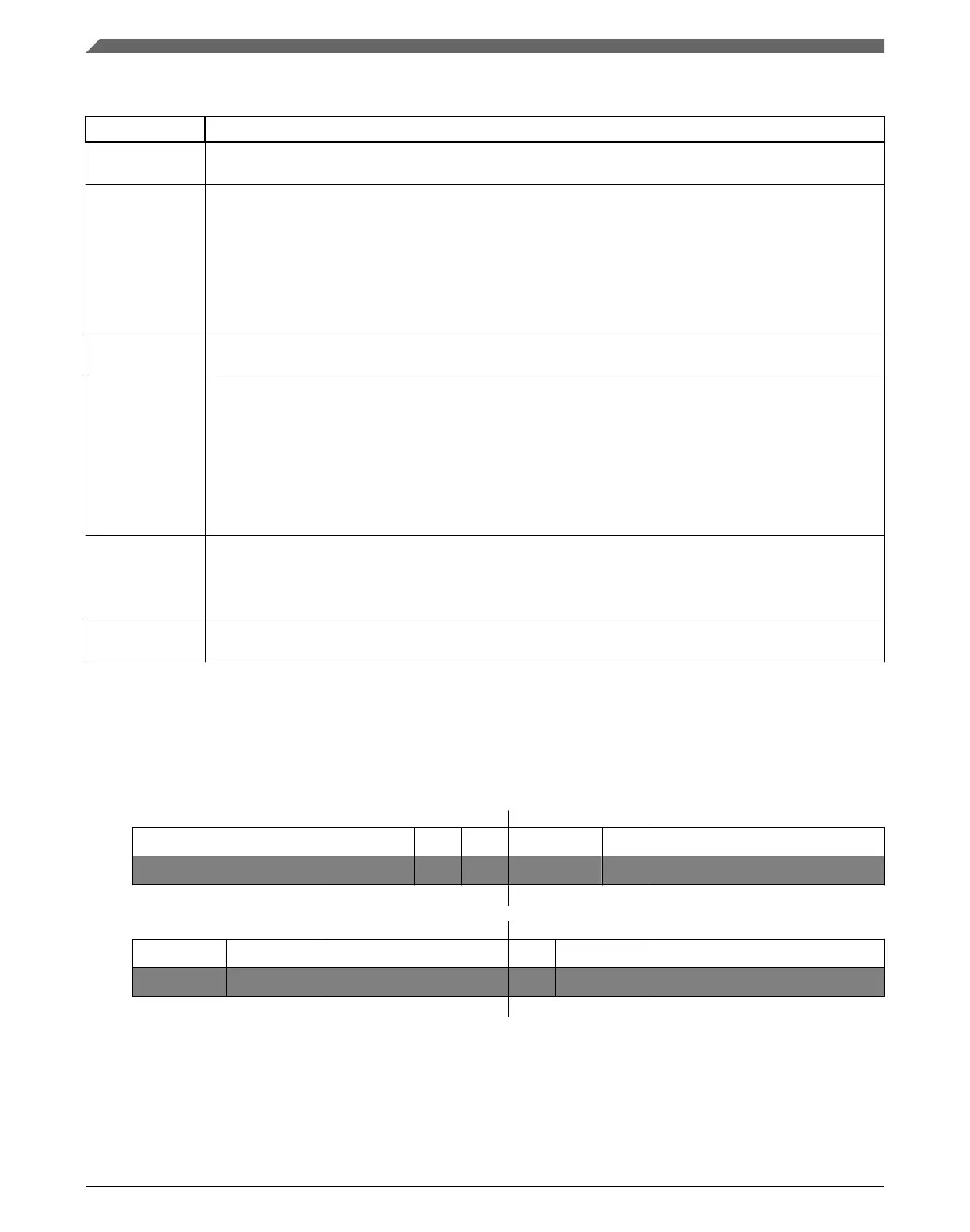

3.3.26 Rx FIFO 0 Status Register (M_CAN_RXF0S)

Address: 0h base + A4h offset = A4h

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R

0 RF0L F0F 0 F0PI

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bit

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

0 F0GI 0 F0FL

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Memory Map and Register Description

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

62 Freescale Semiconductor, Inc.

Loading...

Loading...