3.3 Memory Map and Register Description

After hardware reset, the registers of the M_CAN hold the reset values. Additionally the

Bus_Off state is reset and the M_CAN Tx is set to recessive (HIGH). The value 0x0001

(CCCR[INIT] = 1) in the CC Control Register enables software initialization. The

M_CAN does not influence the CAN bus until the CPU resets CCCR[INIT] to 0.

The M_CAN module allocates an address space of 256 bytes. All registers are organized

as 32-bit registers. The M_CAN is accessible by the CPU using a data width of 8-bit

(byte access), 16-bit (half-word access), or 32-bit (word access).

The CPU has write access to Protected Write registers and fields when both CCCR[CCE]

is 1 and CCCR[INIT] is 1.

There is a delay from writing to a command register until the update of the related status

register bits due to clock domain crossing.

CAUTION

Any write access to reserved or not implemented registers in

the slot assigned by to the M_CAN IP will not generate any bus

access error.

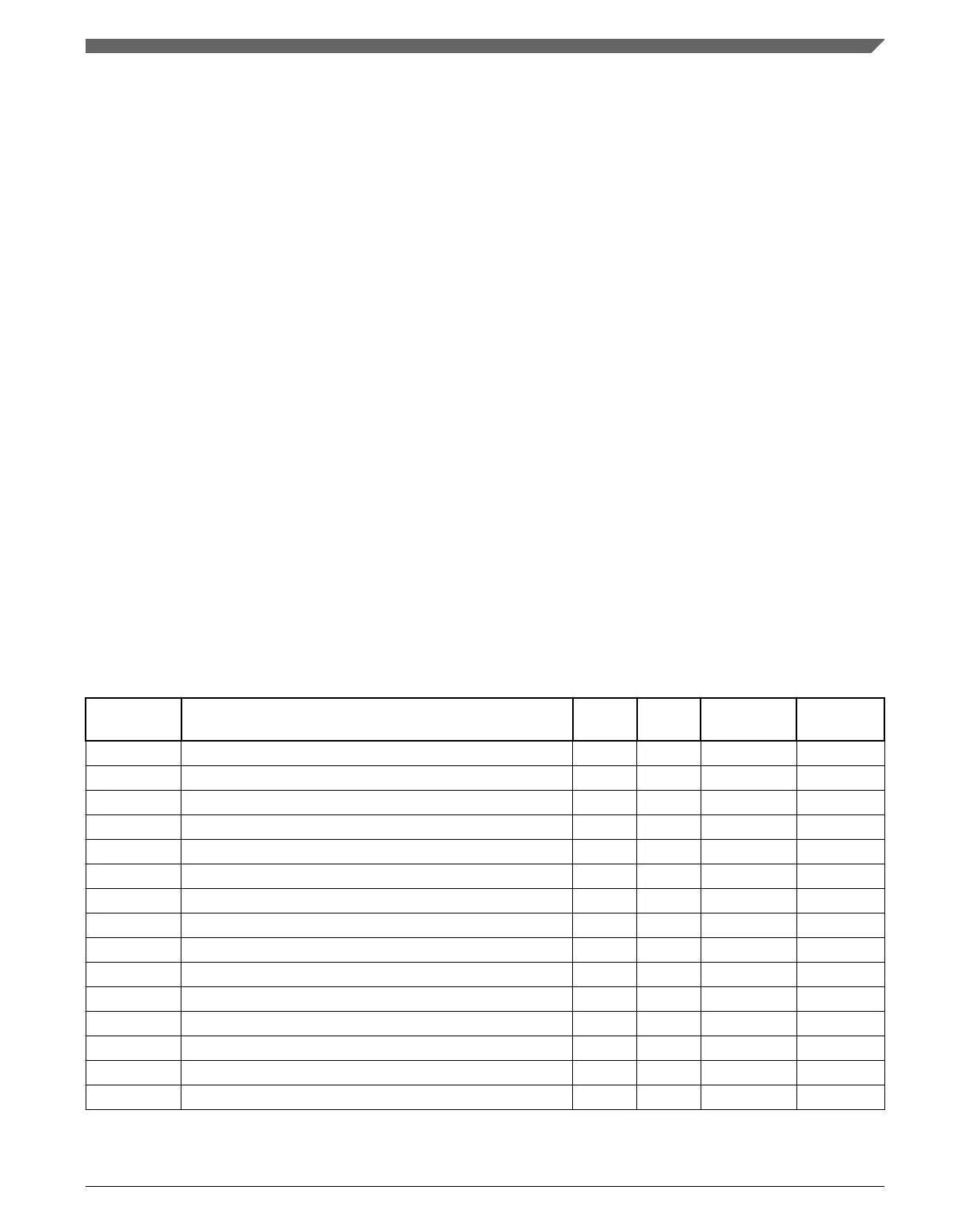

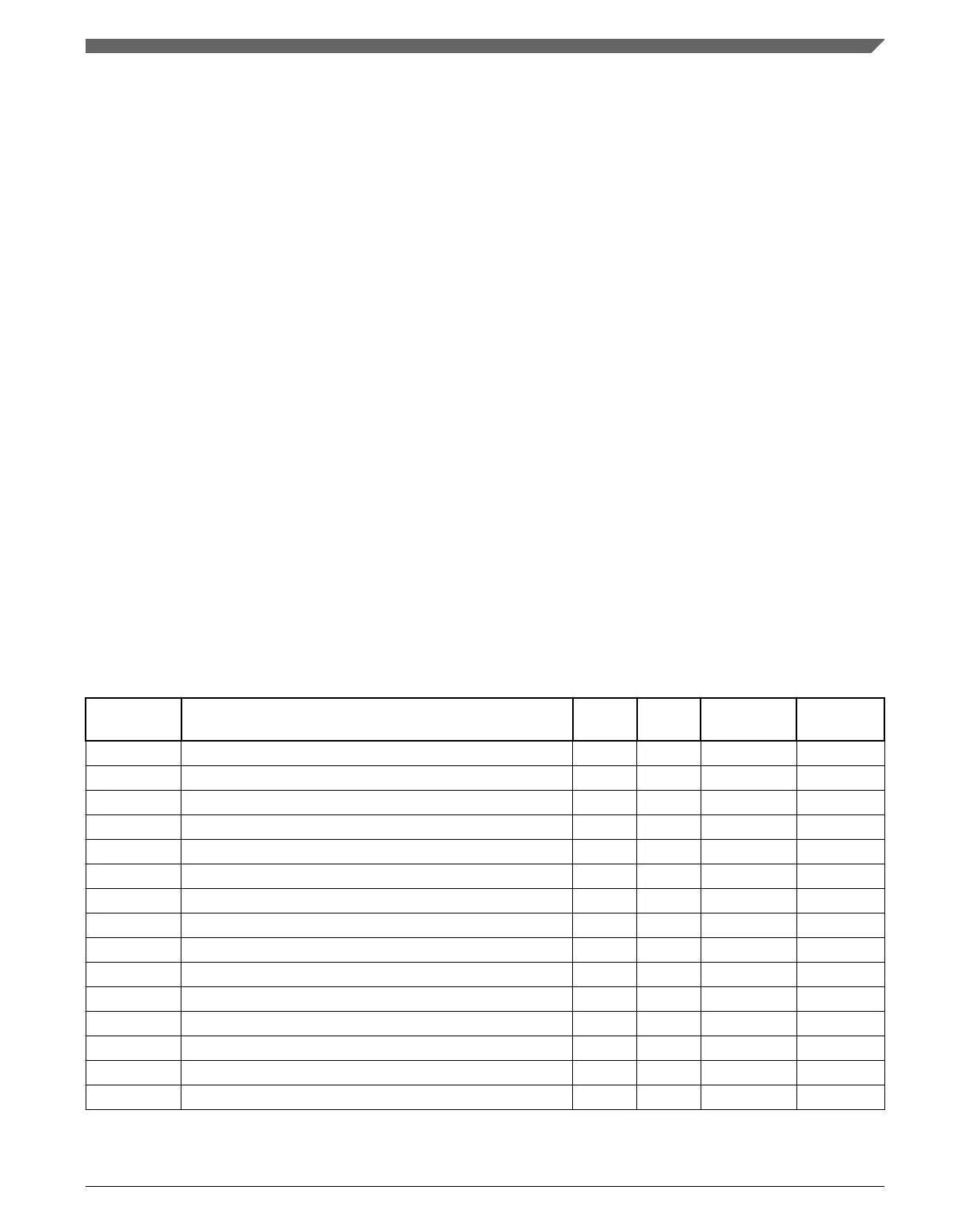

M_CAN memory map

Address

offset (hex)

Register name

Width

(in bits)

Access Reset value

Section/

page

0 Core Release Register (M_CAN_CREL) 32 R See section 3.3.1/28

4 Endian Register (M_CAN_ENDN) 32 R 8765_4321h 3.3.2/29

C Fast Bit Timing and Prescaler Register (M_CAN_FBTP) 32 R/W 0000_0A33h 3.3.3/30

10 Test Register (M_CAN_TEST) 32 R/W See section 3.3.4/32

14 RAM Watchdog Register (M_CAN_RWD) 32 R/W 0000_0000h 3.3.5/33

18 CC Control Register (M_CAN_CCCR) 32 R/W 0000_0001h 3.3.6/34

1C Bit Timing and Prescaler Register (M_CAN_BTP) 32 R/W 0000_0A33h 3.3.7/36

20 Timestamp Counter Configuration Register (M_CAN_TSCC) 32 R/W 0000_0000h 3.3.8/38

24 Timestamp Counter Value Register (M_CAN_TSCV) 32 w1c 0000_0000h 3.3.9/38

28 Timeout Counter Configuration Register (M_CAN_TOCC) 32 R/W FFFF_0000h 3.3.10/39

2C Timeout Counter Value Register (M_CAN_TOCV) 32 w1c 0000_FFFFh 3.3.11/40

40 Error Counter Register (M_CAN_ECR) 32 R 0000_0000h 3.3.12/41

44 Protocol Status Register (M_CAN_PSR) 32 R 0000_0707h 3.3.13/42

50 Interrupt Register (M_CAN_IR) 32 w1c 0000_0000h 3.3.14/45

54 Interrupt Enable Register (M_CAN_IE) 32 R/W 0000_0000h 3.3.15/49

Table continues on the next page...

Chapter 3 Modular CAN (M_CAN)

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 27

Loading...

Loading...