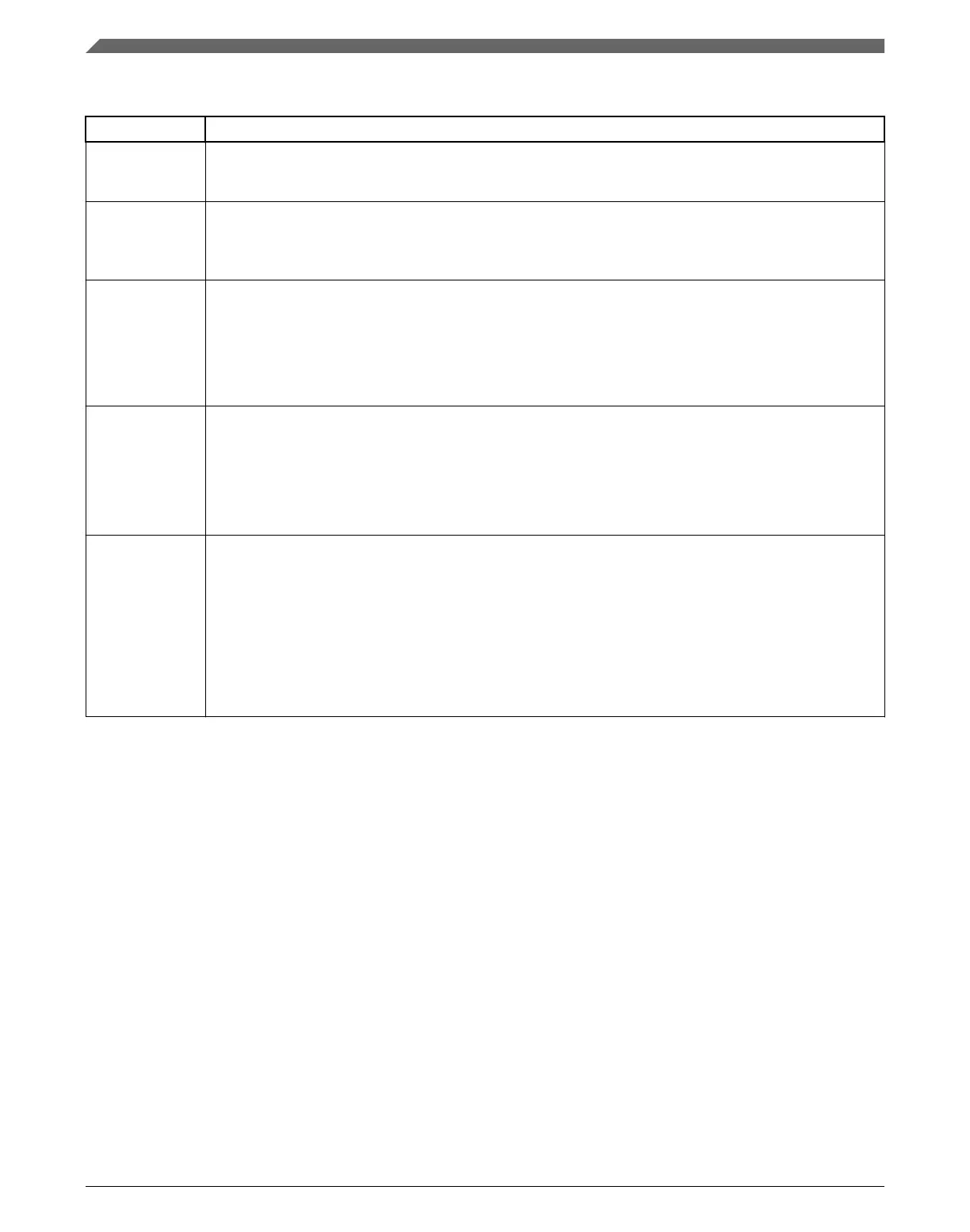

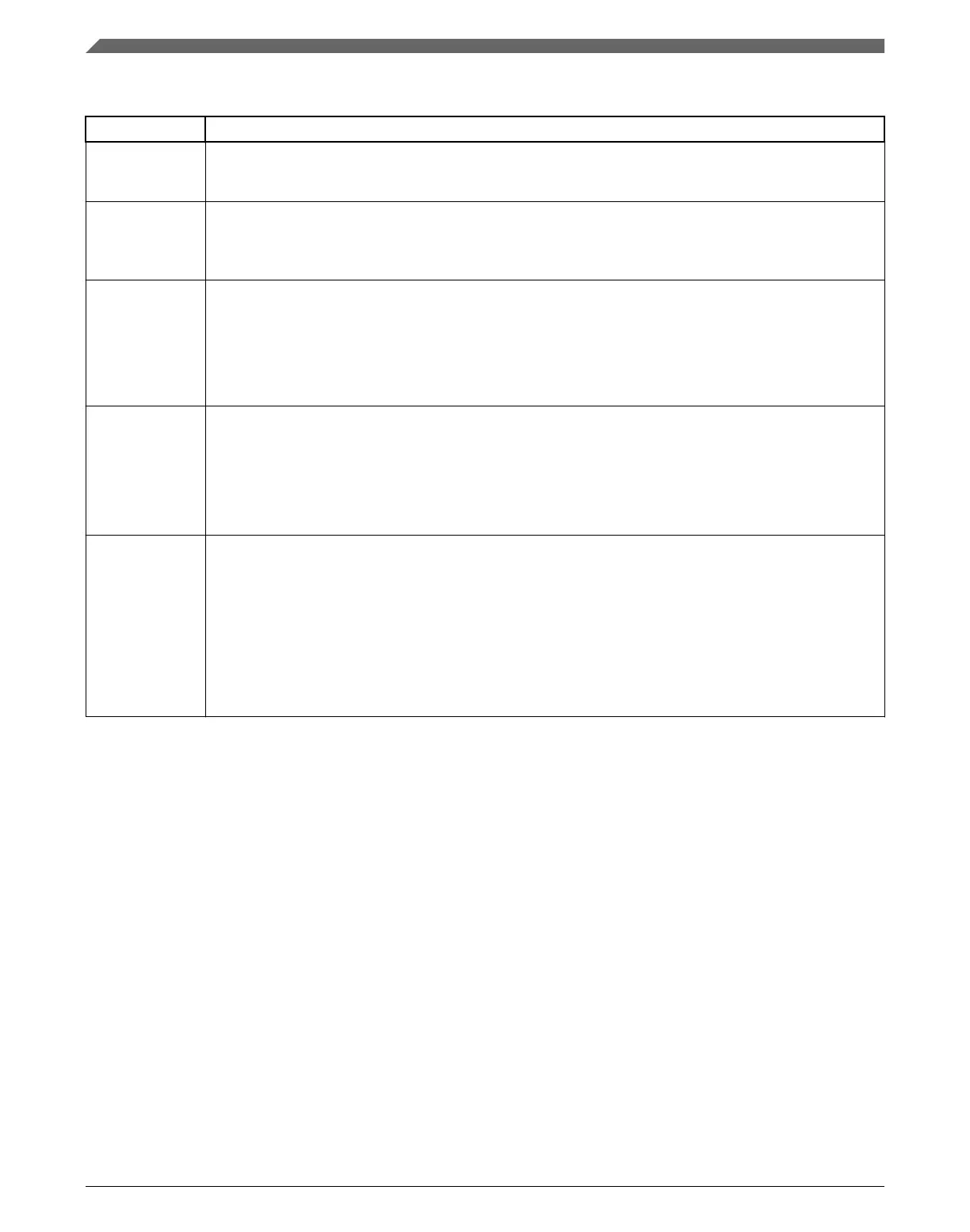

M_CAN_CCCR field descriptions (continued)

Field Description

0 No clock stop is requested

1 Clock stop requested. When clock stop is requested, first INIT and then CSA will be set after all

pending transfer requests have been completed and the CAN bus reached idle.

28

CSA

Clock Stop Acknowledge

0 No clock stop acknowledged

1 M_CAN may be set in power down by stopping M_CAN input clocks

29

ASM

Restricted Operation Mode

Bit ASM is only set by the CPU when both CCE and INIT are set to 1. The bit can be reset by the CPU at

any time.

0 Normal CAN operation

1 Restricted Operation Mode active

30

CCE

Configuration Change Enable

NOTE: This field has Protected Write status.

0 The CPU has no write access to the protected configuration registers

1 The CPU has write access to the protected configuration registers (while CCCR[INIT] = 1)

31

INIT

Initialization

NOTE: Due to the synchronization mechanism between the two clock domains, there may be a delay

until the value written to INIT can be read back. Therefore the programmer has to assure that the

previous value written to INIT has been accepted by reading INIT before setting INIT to a new

value.

0 Normal Operation

1 Initialization is started

3.3.7 Bit Timing and Prescaler Register (M_CAN_BTP)

The CAN bit time may be programed in the range of [4....81] time quanta. The CAN time

quantum may be programmed in the range of [1....1024] M_CAN clock periods. tq =

(BRP + 1) M_CAN clock period.

TSEG1 is the sum of Prop_Seg and Phase_Seg1. TSEG2 is Phase_Seg2.

Therefore the length of the bit time is (programmed values) [TSEG1 + TSEG2 + 3] tq or

(functional values) [Sync_Seg + Prop_Seg + Phase_Seg1 + Phase_Seg2] tq.

The Information Processing Time (IPT) is zero, meaning the data for the next bit is

available at the first clock edge after the sample point.

Memory Map and Register Description

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

36 Freescale Semiconductor, Inc.

Loading...

Loading...