M_CAN_ENDN field descriptions

Field Description

0–31

ETV

Endianness Test Value

The endianness test value is 0x87654321.

3.3.3 Fast Bit Timing and Prescaler Register (M_CAN_FBTP)

The CAN bit time may be programed in the range of 4 to 25 time quanta. The CAN time

quantum may be programmed in the range of 1 to 32 M_CAN clock periods. tq = (FBRP

+ 1) M_CAN clock period.

FTSEG1 is the sum of Prop_Seg and Phase_Seg1. FTSEG2 is Phase_Seg2. Therefore the

length of the bit time is (programmed values) [FTSEG1 + FTSEG2 + 3] tq or (functional

values) [Sync_Seg + Prop_Seg + Phase_Seg1 + Phase_Seg2] tq.

The Information Processing Time (IPT) is zero, meaning the data for the next bit is

available at the first clock edge after the sample point.

NOTE

With a M_CAN clock of 8 MHz, the reset value of

0x00000A33 configures the M_CAN for a fast bit rate of 500

kbit/s.

The bit rate configured for the CAN FD data phase via FBTP

must be higher or equal to the bit rate configured for the

arbitration phase via BTP.

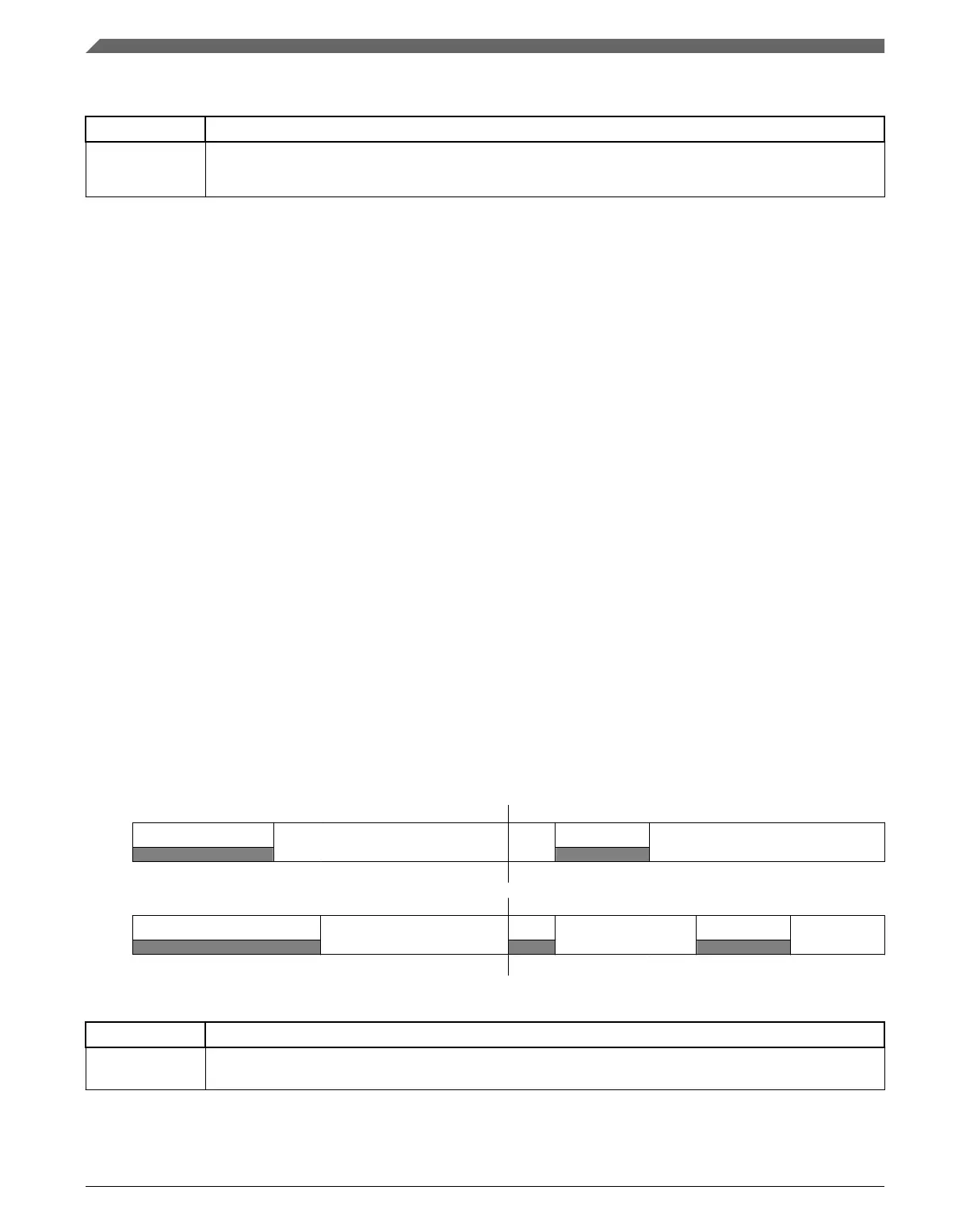

Address: 0h base + Ch offset = Ch

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R

0

TDCO TDC

0

FBRP

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

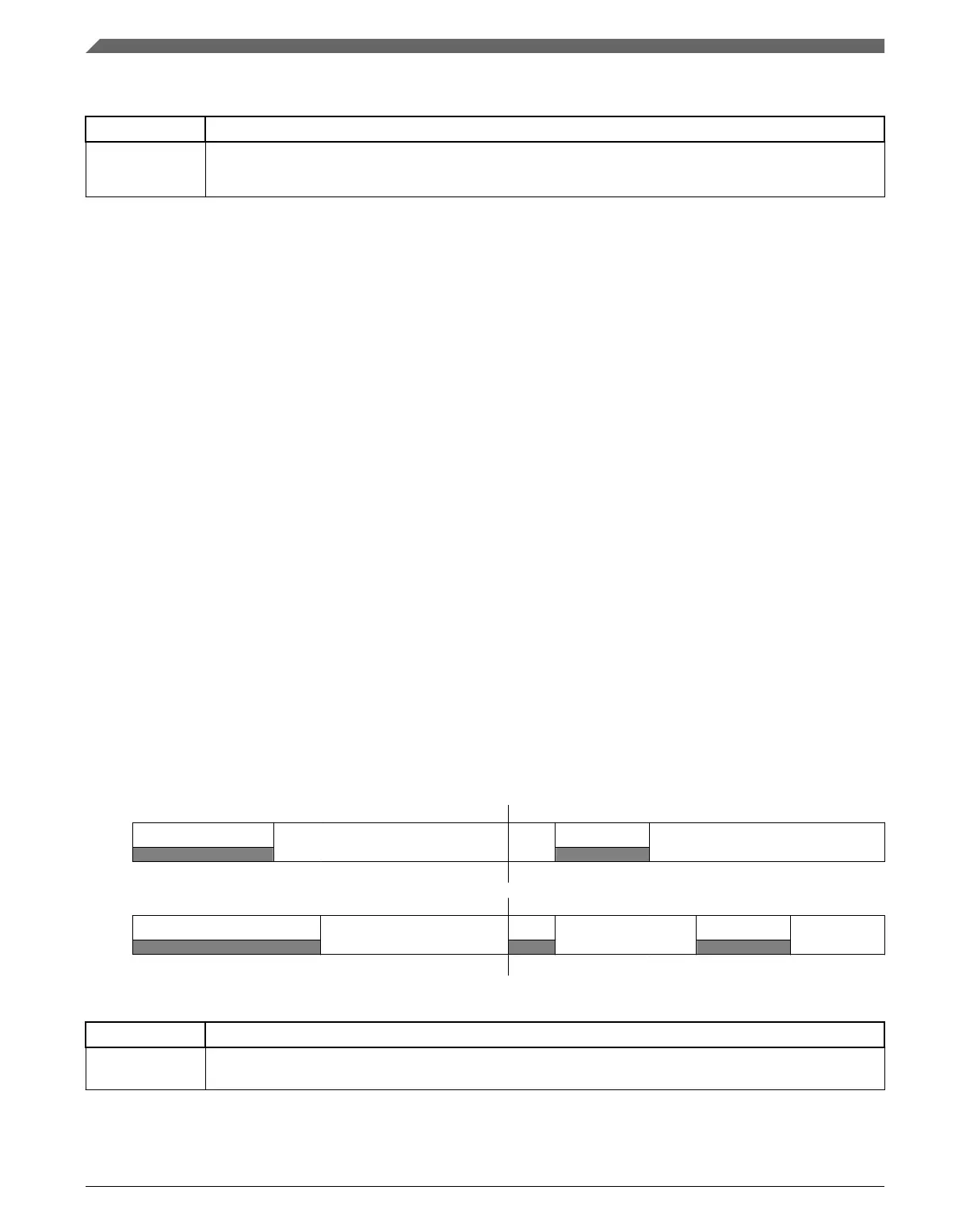

Bit

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

0

FTSEG1

0

FTSEG2

0

FSJW

W

Reset

0 0 0 0 1 0 1 0 0 0 1 1 0 0 1 1

M_CAN_FBTP field descriptions

Field Description

0–2

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

Table continues on the next page...

Memory Map and Register Description

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

30 Freescale Semiconductor, Inc.

Loading...

Loading...