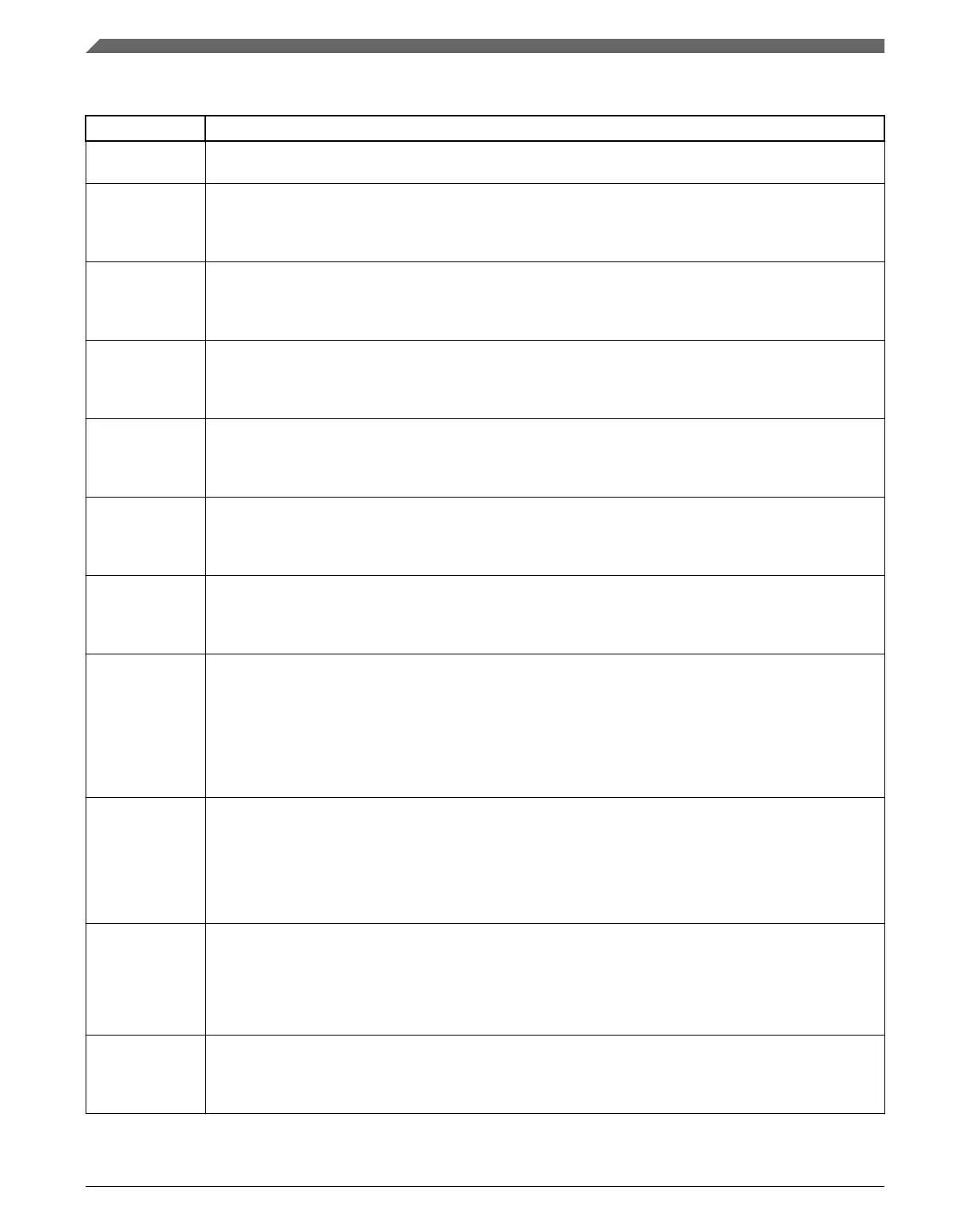

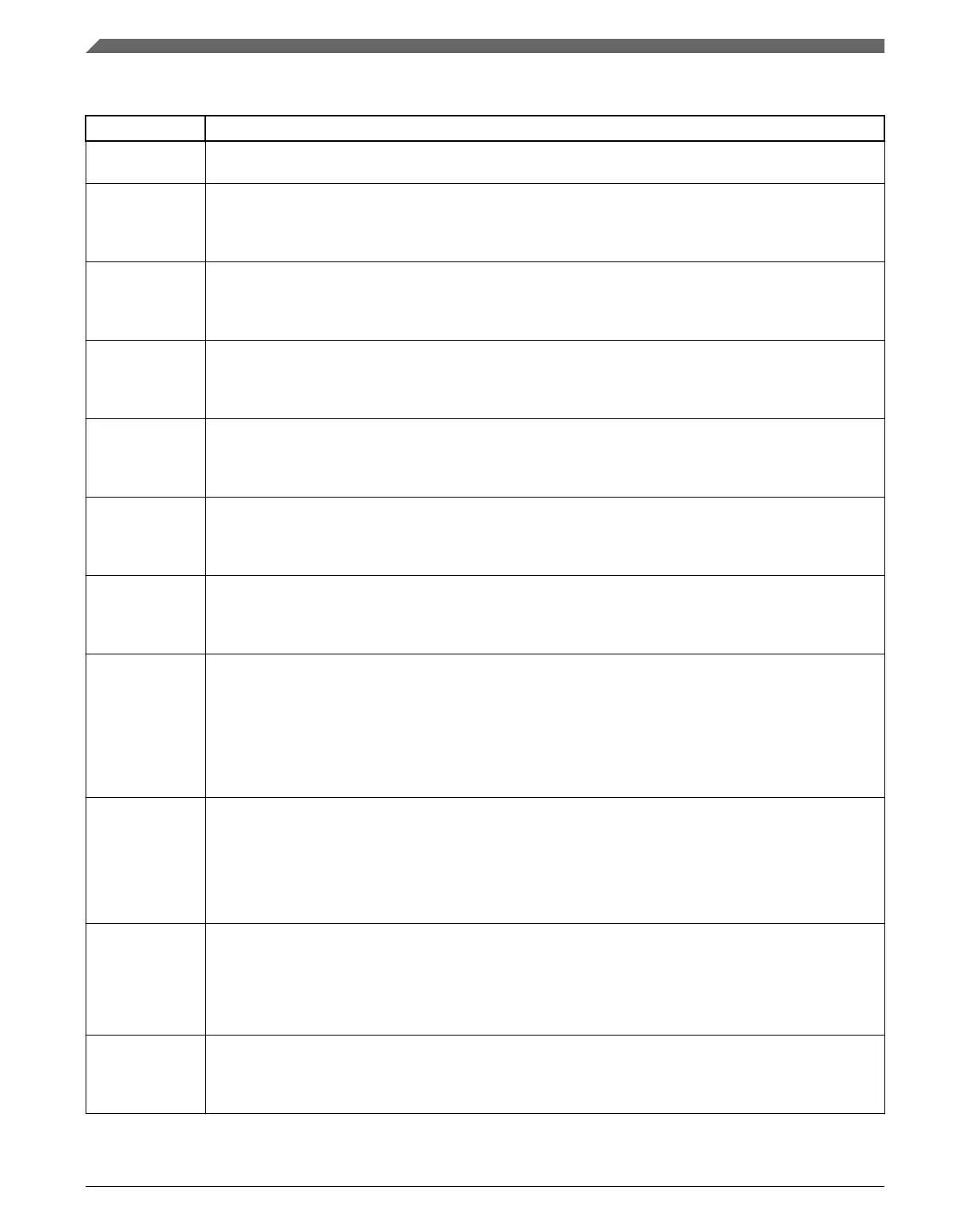

M_CAN_IR field descriptions (continued)

Field Description

0 No Bit Error detected

1 Device wanted to send a rec / dom level, but monitored bus level was dom / rec

4

CRCE

CRC Error

0 No CRC Error detected

1 Received CRC did not match the calculated CRC

5

WDI

Watchdog Interrupt

0 No Message RAM Watchdog event occurred

1 Message RAM Watchdog event due to missing READY

6

BO

Bus_Off Status

0 Bus_Off status unchanged

1 Bus_Off status changed

7

EW

Warning Status

0 Error_Warning status unchanged

1 Error_Warning status changed

8

EP

Error Passive

0 Error_Passive status unchanged

1 Error_Passive status changed

9

ELO

Error Logging Overflow

0 CAN Error Logging Counter did not overflow

1 Overflow of CAN Error Logging Counter occurred

10

BEU

Bit Error Uncorrected

Message RAM bit error detected, uncorrected. Controlled by an external ECC logic attached to the

Message RAM. An uncorrected Message RAM bit error sets CCCR[INIT] to 1. This is done to avoid

transmission of corrupted data.

0 No bit error detected when reading from Message RAM

1 Bit error detected, uncorrected (e.g. parity logic)

11

BEC

Bit Error Corrected

Message RAM bit error detected and corrected. Controlled by an external parity ECC logic attached to the

Message RAM.

0 No bit error detected when reading from Message RAM

1 Bit error detected and corrected (e.g. ECC)

12

DRX

Message stored to Dedicated Rx Buffer

The flag is set whenever a received message has been stored into a dedicated Rx Buffer.

0 No Rx Buffer updated

1 At least one received message stored into a Rx Buffer

13

TOO

Timeout Occurred

0 No timeout

1 Timeout reached

Table continues on the next page...

Memory Map and Register Description

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

46 Freescale Semiconductor, Inc.

Loading...

Loading...