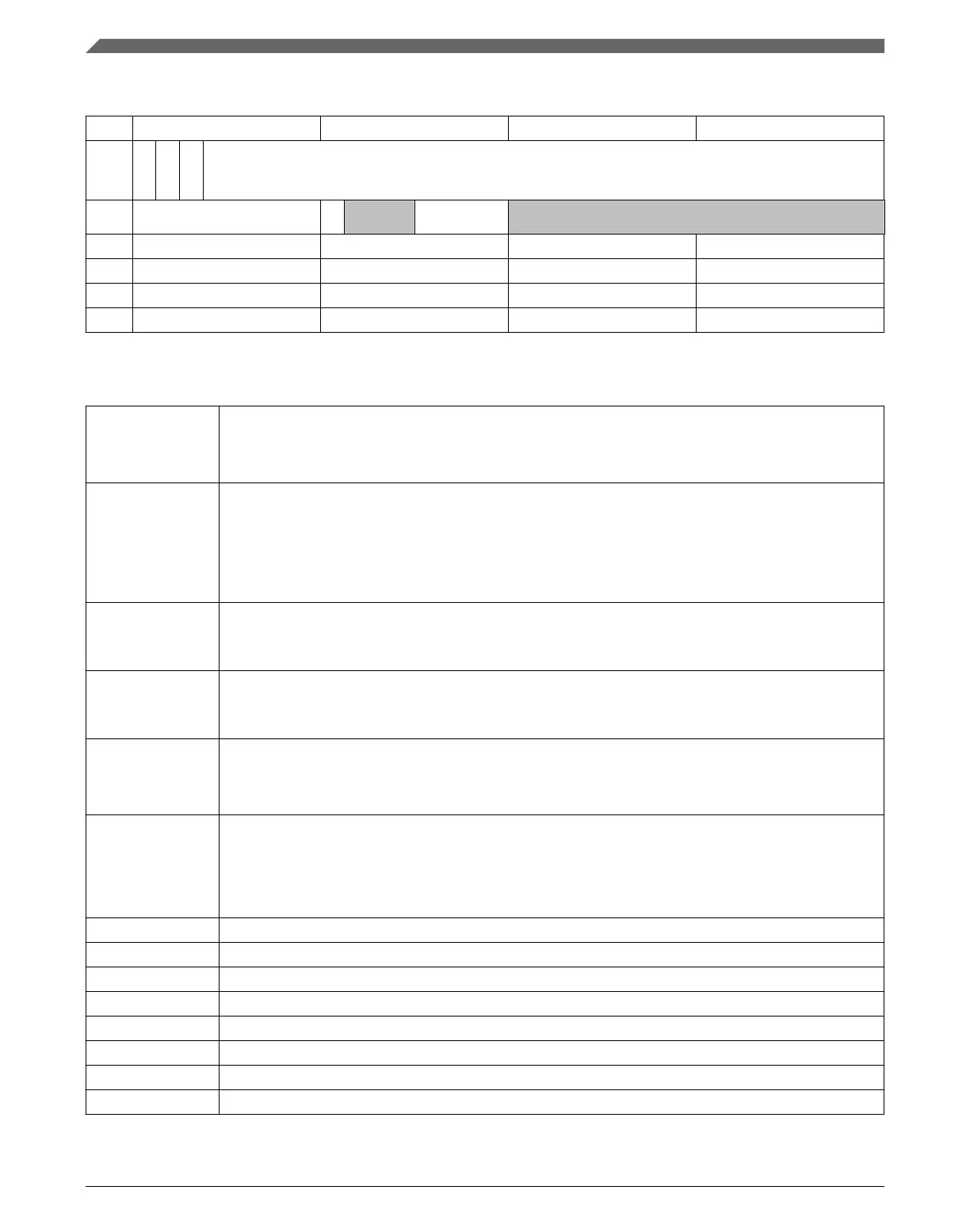

Table 3-50. Tx Buffer Element

31 24 23 16 15 8 7 0

T0

re

s

X

T

D

R

T

R

ID[28:0]

T1

MM[7:0]

EF

C

res DLC[3:0] res

T2 DB3[7:0] DB2[7:0] DB1[7:0] DB0[7:0]

T3 DB7[7:0] DB6[7:0] DB5[7:0] DB4[7:0]

... ... ... ... ...

Tn DBm[7:0] DBm-1[7:0] DBm-2[7:0] DBm-3[7:0]

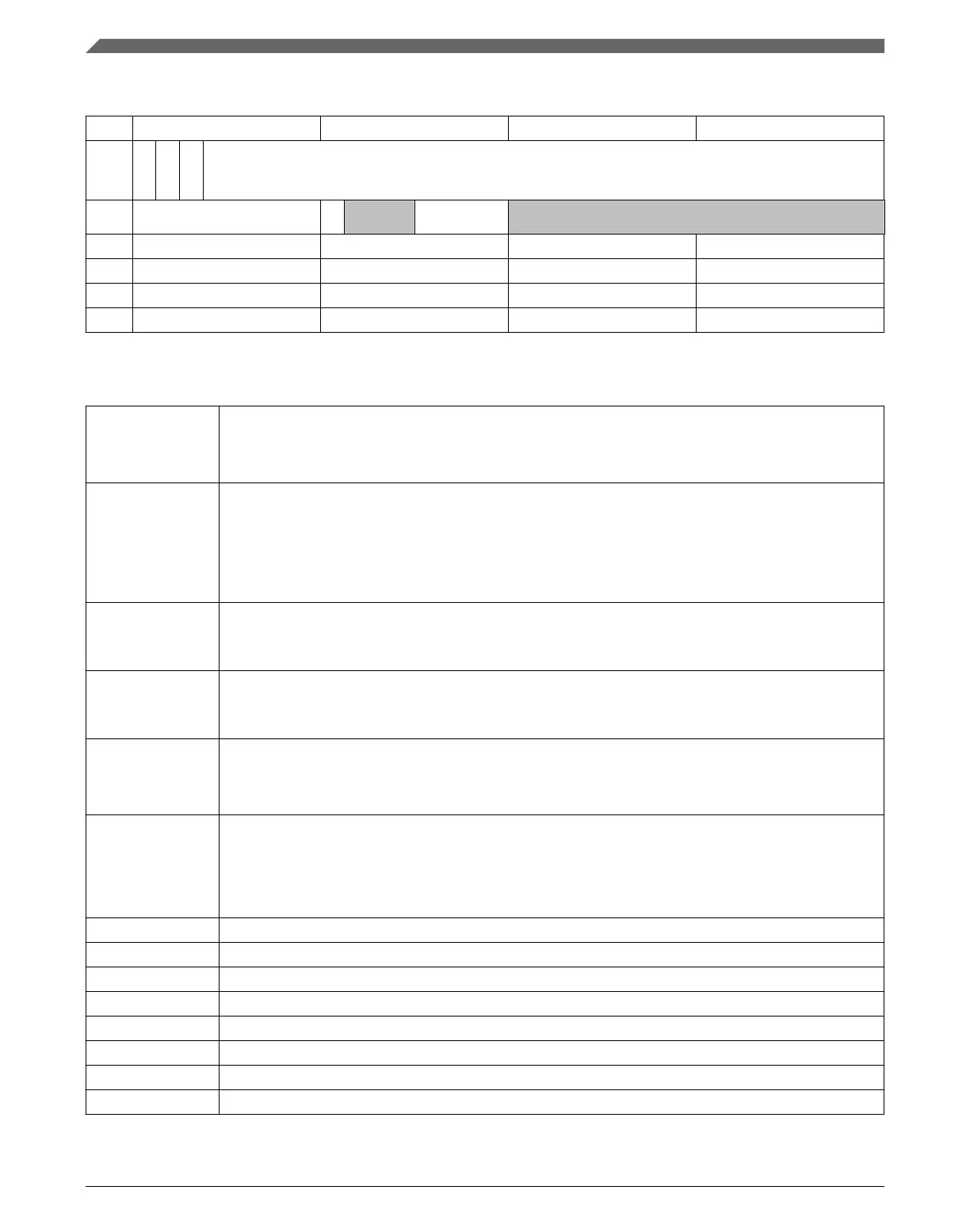

Table 3-51. Tx Buffer Element Description

T0 Bit 30 XTD: Extended Identifier

0 11-bit standard identifier

1 29-bit extended identifier

T0 Bit 29 RTR: Remote Transmission Request

0 Transmit data frame

1 Transmit remote frame

NOTE: When RTR = 1, the M_CAN transmits a remote frame according to ISO11898-1, even if

CCCR[CME] enables the transmission in CAN FD format.

T0 Bit 28:0 ID[28:0]: Identifier

Standard or extended identifier depending on bit XTD. A standard identifier has to be written to

ID[28:18].

T1 Bits 31:24 MM[7:0]: Message Marker

Written by CPU during Tx Buffer configuration. Copied into Tx Event FIFO element for identification of

Tx message status.

T1 Bit 23 EFC: Event FIFO Control

0 Do not store Tx events

1 Store Tx events

T1 Bits 19:16 DLC[3:0]: Data Length Code

0-8 CAN + CAN FD: Transmit frame has 0-8 data bytes

9-15 CAN: Transmit frame has 8 data bytes

9-15 CAN FD: Transmit frame has 12/16/20/24/32/48/64 data bytes

T2 Bits 31:24 DB3[7:0]: Data Byte 3

T2 Bits 23:16 DB2[7:0]: Data Byte 2

T2 Bits 15:8 DB1[7:0]: Data Byte 1

T2 Bits 7:0 DB0[7:0]: Data Byte 0

T3 Bits 31:24 DB7[7:0]: Data Byte 7

T3 Bits 23:16 DB6[7:0]: Data Byte 6

T3 Bits 15:8 DB5[7:0]: Data Byte 5

T3 Bits 7:0 DB4[7:0]: Data Byte 4

Table continues on the next page...

Message RAM

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

82 Freescale Semiconductor, Inc.

Loading...

Loading...