161

Sequence Input Instructions Section 3-3

3-3 Sequence Input Instructions

3-3-1 LOAD: LD

Purpose Indicates a logical start and creates an ON/OFF execution condition based on

the ON/OFF status of the specified operand bit.

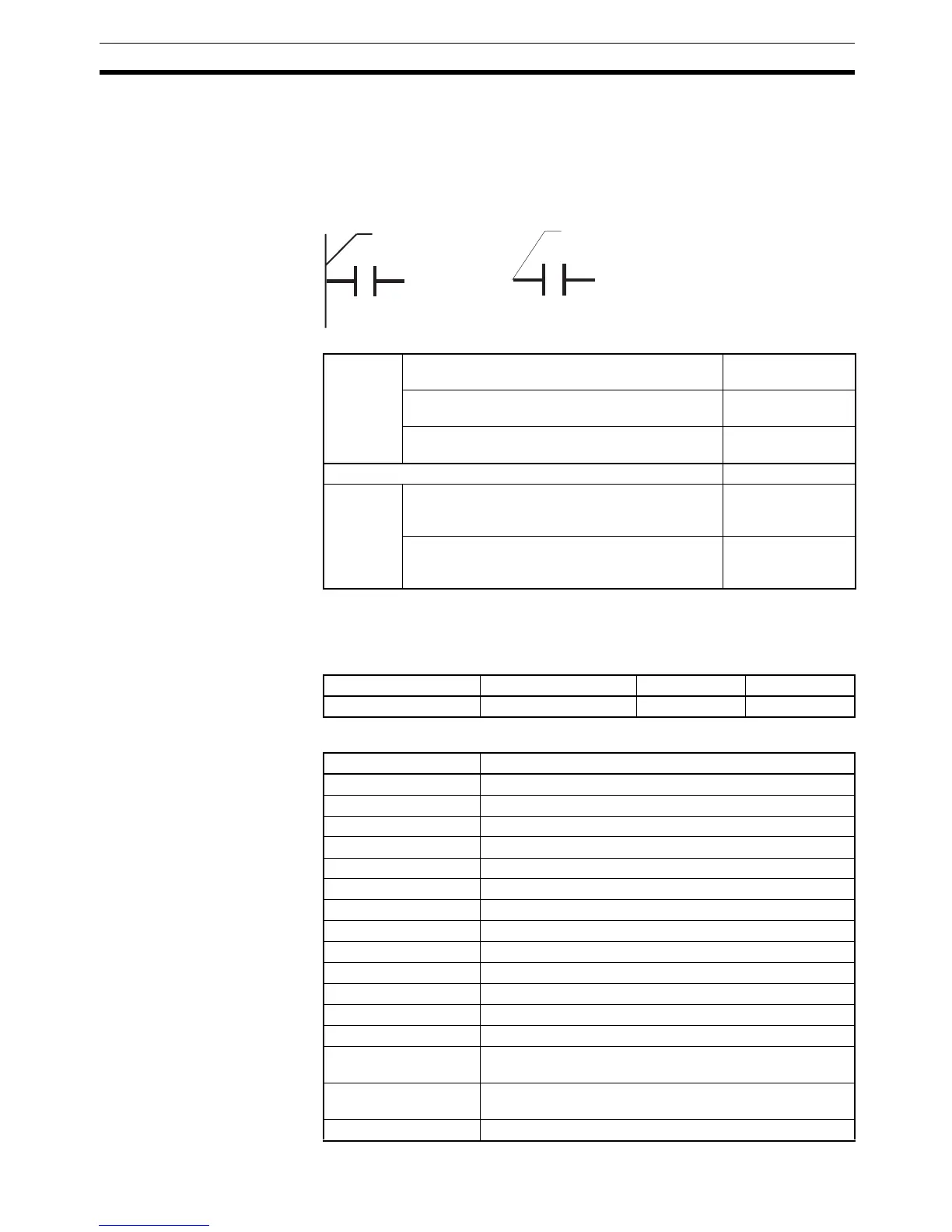

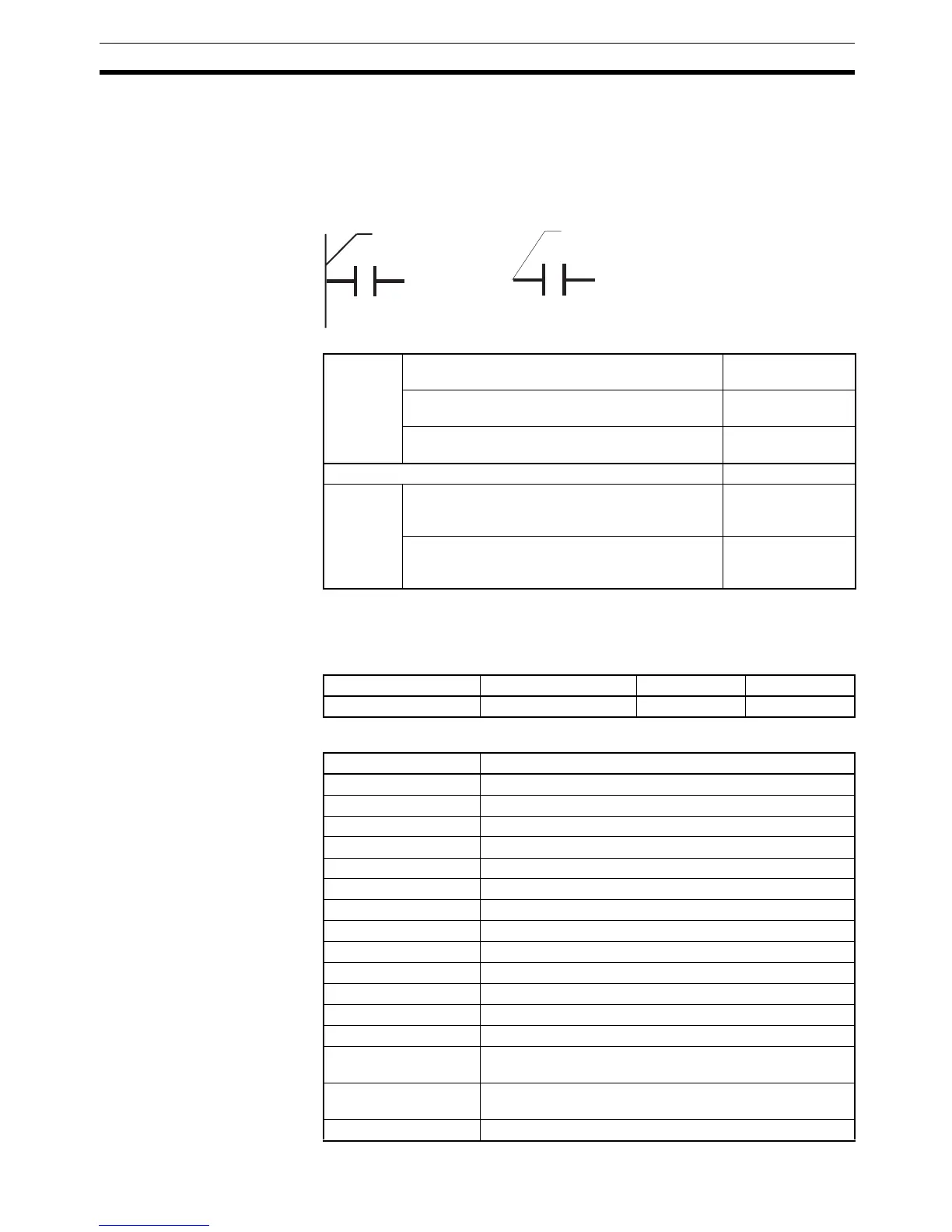

Ladder Symbol

Variations

Note Immediate refreshing is not supported by CS1D CPU Units for Duplex-CPU

Systems.

Applicable Program Areas

Operand Specifications

Bus bar

Starting point of block

Variations Restarts Logic and Creates ON Each Cycle

Operand Bit is ON

LD

Restarts Logic and Creates ON Once for

Upward Differentiation

@LD

Restarts Logic and Creates ON Once for

Downward Differentiation

%LD

Immediate Refreshing Specification (See note.) !LD

Combined

Variations

Refreshes Input Bit, Restarts Logic, and

Creates ON Once for Upward Differentiation

(See note.)

!@LD

Refreshes Input Bit, Restarts Logic, and

Creates ON Once for Downward Differentiation

(See note.)

!%LD

Block program areas Step program areas Subroutines Interrupt tasks

OK OK OK OK

Area LD operand bit

CIO Area CIO 000000 to CIO 614315

Work Area W00000 to W51115

Holding Bit Area H00000 to H51115

Auxiliary Bit Area A00000 to A95915

Timer Area T0000 to T4095

Counter Area C0000 to C4095

Task Flag Area TK0000 to TK0031

Condition Flags ER, CY, N, OF, UF, >, =, <, >=, <>, <=, A1, A0

Clock Pulses 0.02 s, 0.1 s, 0.2 s, 1 s, 1 min

TR Area TR0 to TR15

DM Area ---

EM Area without bank ---

EM Area with bank ---

Indirect DM/EM

addresses in binary

---

Indirect DM/EM

addresses in BCD

---

Constants ---

Loading...

Loading...