394

Data Shift Instructions Section 3-9

Note All words in the shift register must be in the same area.

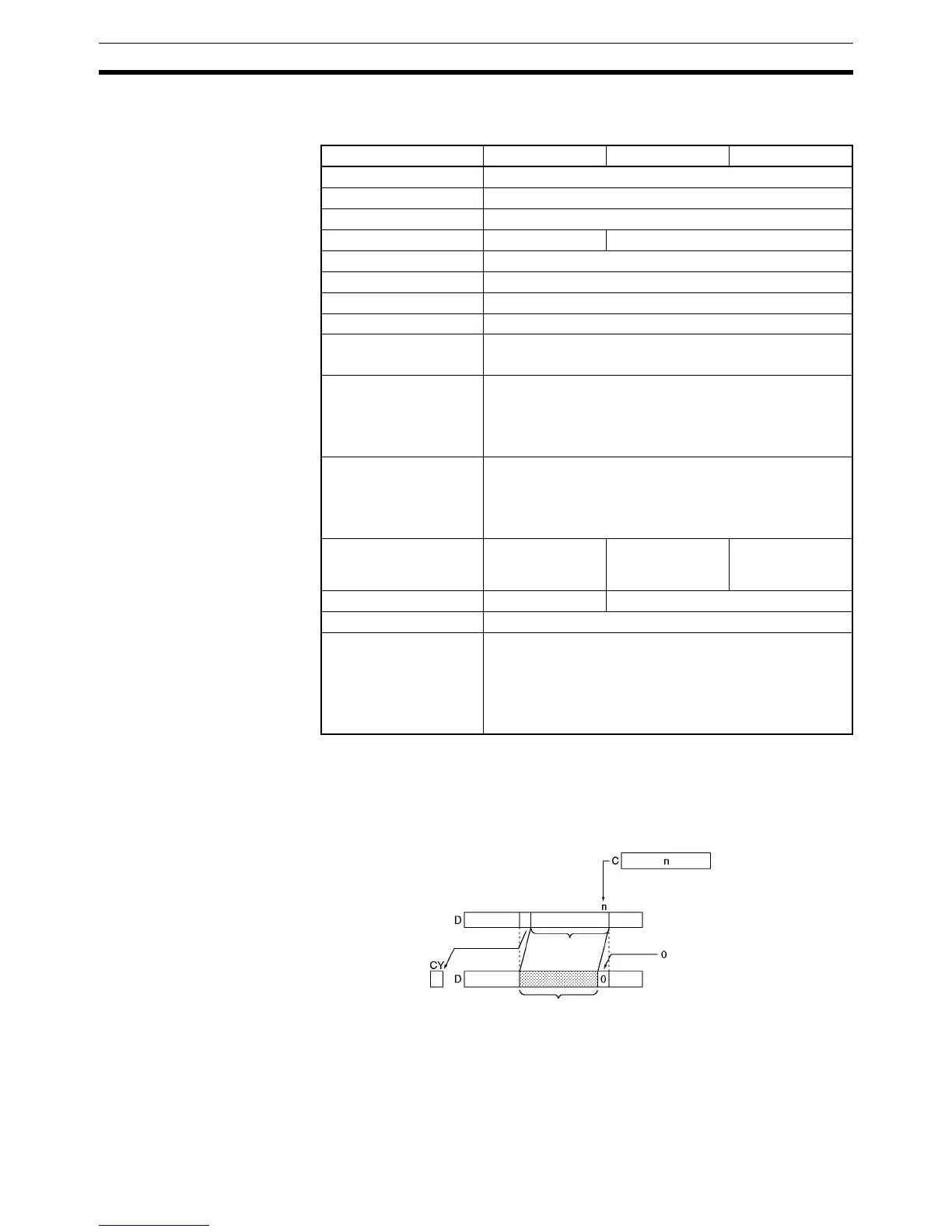

Operand Specifications

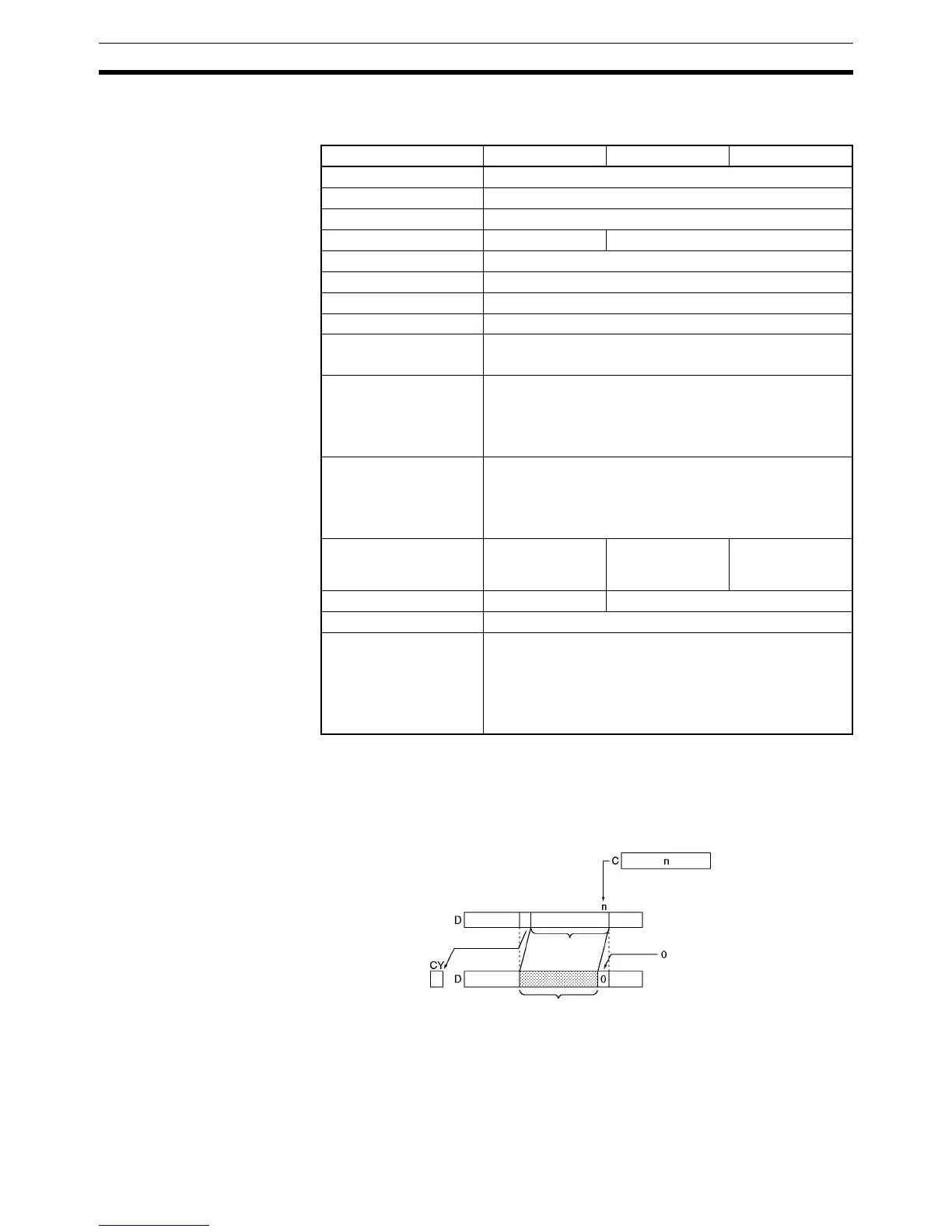

Description NSFL(578) shifts the specified number of bits by the shift data length (N) from

the beginning bit (C) in the rightmost word, as designated by D one bit to the

left (towards the leftmost word and the leftmost bit). “0” is place into the begin-

ning bit and the contents of the leftmost bit in the shift area are shifted to the

Carry Flag (CY).

Area DCN

CIO Area CIO 0000 to CIO 6143

Work Area W000 to W511

Holding Bit Area H000 to H511

Auxiliary Bit Area A448 to A959 A000 to A959

Timer Area T0000 to T4095

Counter Area C0000 to C4095

DM Area D00000 to D32767

EM Area without bank E00000 to E32767

EM Area with bank En_00000 to En_32767

(n = 0 to C)

Indirect DM/EM

addresses in binary

@ D00000 to @ D32767

@ E00000 to @ E32767

@ En_00000 to @ En_32767

(n = 0 to C)

Indirect DM/EM

addresses in BCD

*D00000 to *D32767

*E00000 to *E32767

*En_00000 to *En_32767

(n = 0 to C)

Constants --- #0000 to #000F

(binary) or &0 to

&15

#0000 to #FFFF

(binary) or &0 to

&65535

Data Registers --- DR0 to DR15

Index Registers ---

Indirect addressing

using Index Registers

,IR0 to ,IR15

–2048 to +2047 ,IR0 to –2048 to +2047 ,IR15

DR0 to DR15, IR0 to IR15

,IR0+(++) to ,IR15+(++)

,–(– –)IR0 to, –(– –)IR15

Shifts one bit to the left

N−1 bit

N−1 bit

Loading...

Loading...