561

Logic Instructions Section 3-13

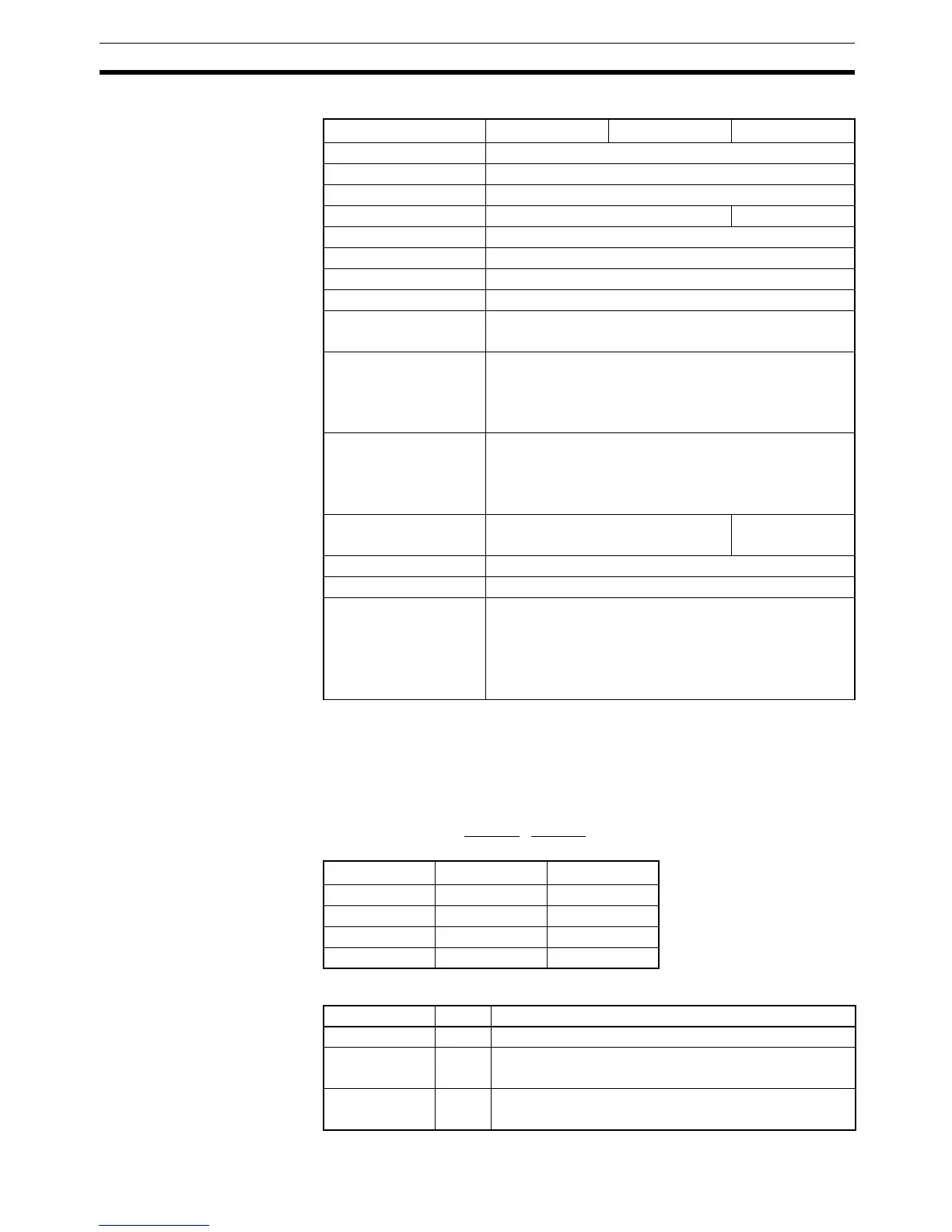

Operand Specifications

Description XNRL(613) takes the logical exclusive NOR of data specified in I

1

and I

2

and

outputs the result to R, R+1.

• When the content of any of the corresponding bits in I

1,

I

1

+1, I

2,

and

I

2

+1are different, a 0 will be output to the corresponding bit in R, R+1.

When any of them are the same, a 1 will be output to the corresponding

bit in R, R+1.

(I

1,

I

1

+1), (I

2,

I

2

+1) + (I

1,

I

1

+1), (I

2,

I

2

+1)

→ (R, R+1)

Flags

Area I

1

I

2

R

CIO Area CIO 0000 to CIO 6142

Work Area W000 toW 510

Holding Bit Area H000 to H510

Auxiliary Bit Area A000 to A958 A448 to A958

Timer Area T0000 to T4094

Counter Area C0000 to C4094

DM Area D00000 to D32766

EM Area without bank E00000 to E32766

EM Area with bank En_00000 to En_32766

(n = 0 to C)

Indirect DM/EM

addresses in binary

@ D00000 to @ D32767

@ E00000 to @ E32767

@ En_00000 to @ En_32767

(n = 0 to C)

Indirect DM/EM

addresses in BCD

*D00000 to *D32767

*E00000 to *E32767

*En_00000 to *En_32767

(n = 0 to C)

Constants #00000000 to #FFFFFFFF

(binary)

---

Data Registers ---

Index Registers ---

Indirect addressing

using Index Registers

,IR0 to ,IR15

–2048 to +2047 ,IR0 to –2048 to +2047 ,IR15

DR0 to DR15, IR0 to IR15

,IR0+(++) to ,IR15+(++)

,–(– –)IR0 to, –(– –)IR15

I

1,

I

1

+1 I

2,

I

2

+1 R, R+1

111

100

010

001

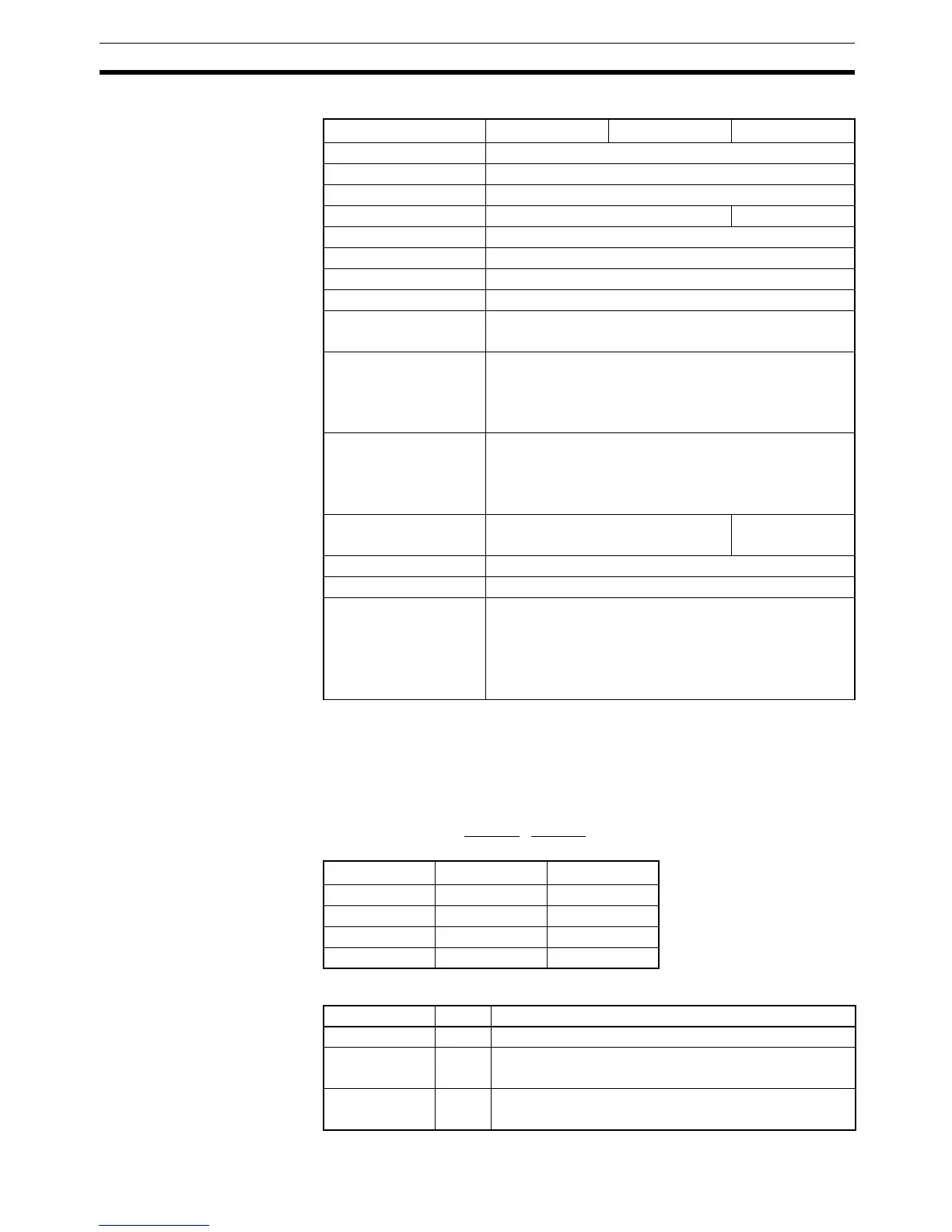

Name Label Operation

Error Flag ER OFF

Equals Flag = ON when the result is 0.

OFF in all other cases.

Negative Flag N ON when the leftmost bit of R is 1.

OFF in all other cases.

Loading...

Loading...