853

Interrupt Control Instructions Section 3-20

■ Clearing/Retaining High-speed Counter Interrupts (CJ1M Only)

Operand Specifications

Description Depending on the value of N, CLI(691) clears the specified recorded I/O inter-

rupts, sets the time before execution of the first scheduled interrupt, or clears

the specified recorded high-speed counter interrupts (CJM1 CPU Units only).

With the CJ1M, it can also be used to clear interrupts for the high-speed

counters.

N = 0 to 3, or 6 to 9: Clearing Interrupt Inputs

CLI(691) clears a recorded interrupt input specified by N, when the corre-

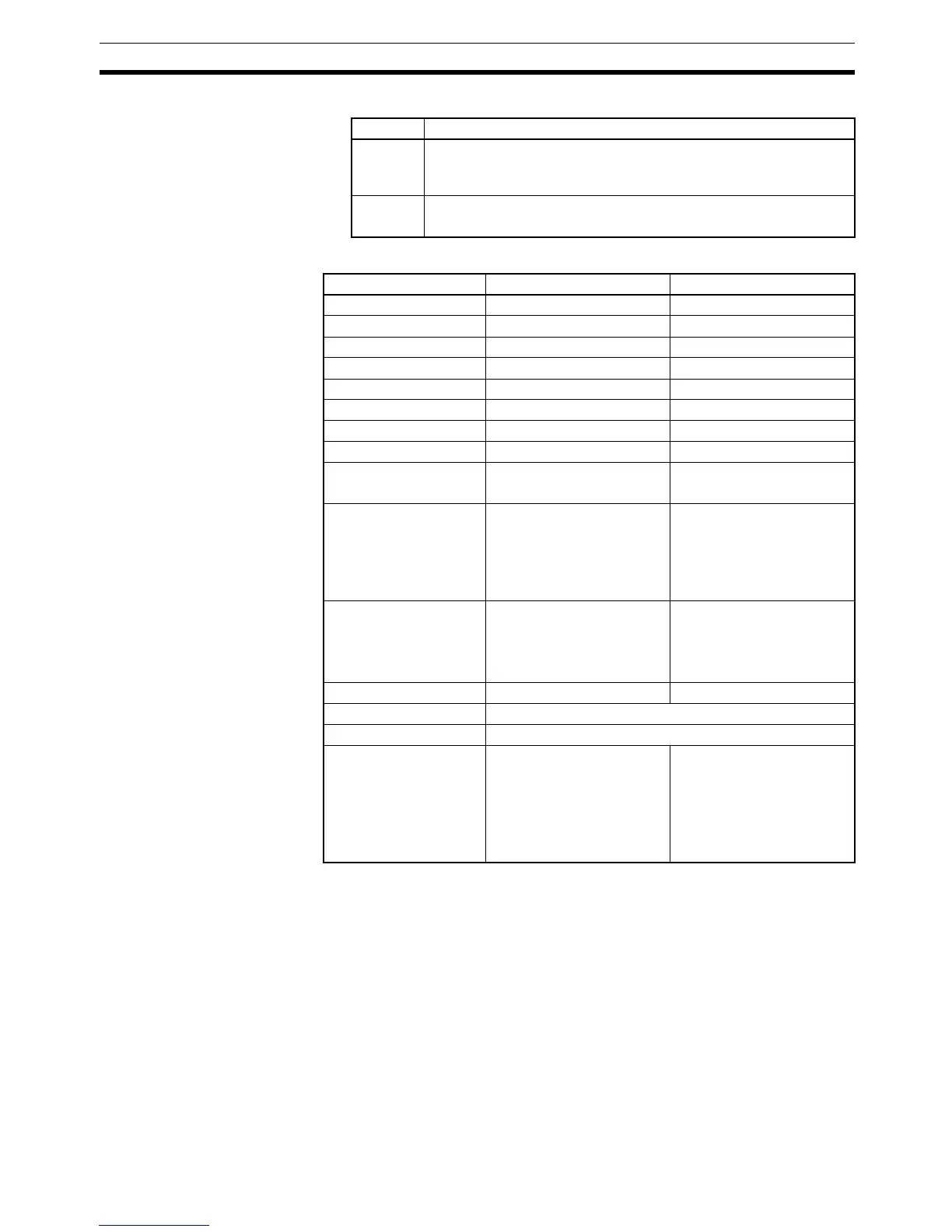

Operand Contents

N Specify the high-speed counter input.

10: High-speed counter input 0 (interrupt task 2)

11: High-speed counter input 1 (interrupt task 3)

C 0000 hex: Retain the recorded interrupt.

0001 hex: Clear the recorded interrupt.

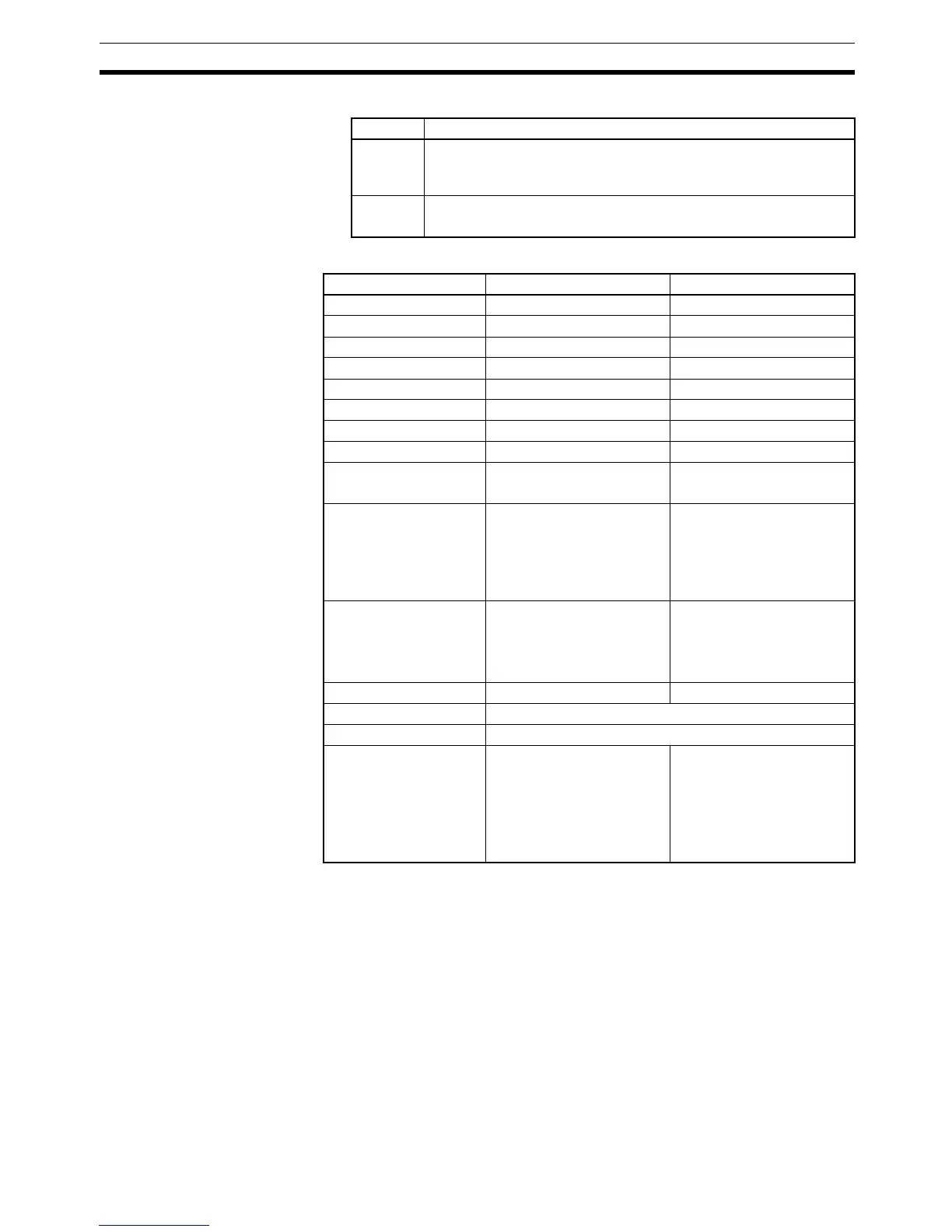

Area N C

CIO Area --- CIO 0000 to CIO 6143

Work Area --- W000 to W511

Holding Bit Area --- H000 to H511

Auxiliary Bit Area --- A000 to A959

Timer Area --- T0000 to T4095

Counter Area --- C0000 to C4095

DM Area --- D00000 to D32767

EM Area without bank --- E00000 to E32767

EM Area with bank --- En_00000 to En_32767

(n = 0 to C)

Indirect DM/EM

addresses in binary

--- @ D00000 to @ D32767

@ E00000 to @ E32767

@ En_00000 to

@ En_32767

(n = 0 to C)

Indirect DM/EM

addresses in BCD

--- *D00000 to *D32767

*E00000 to *E32767

*En_00000 to *En_32767

(n = 0 to C)

Constants --- DR0 to DR15

Data Registers Specified values only

Index Registers ---

Indirect addressing

using Index Registers

--- ,IR0 to ,IR15

–2048 to +2047, IR0 to –

2048 to +2047, IR15

DR0 to DR15, IR0 to IR15

,IR0+(++) to ,IR15+(++)

,–(– –) IR0 to, –(– –) IR15

Loading...

Loading...