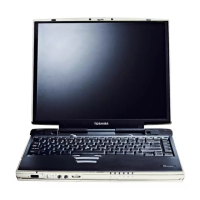

1.2 System Unit Block Diagram 1 Hardware Overview

TECRA 9100 Maintenance Manual (960-347) 1-9

The system unit is composed of the following major components:

Processor

• Intel Mobile Pentium 4 Processor 1.70GHz

– Processor core speed: 1.70GHz (Performance Mode at 1.30V) and

1.20GHz (Battery Optimized Mode at 1.20V)

– Processor bus speed: 400MHz

– Integrated L1 cache memory: 12KB instruction cache and 8KB write-

back data cache, 4-way set associative

– Integrated L2 cache memory: 512KB ECC protected cache data array,

8-way set associative

– Integrated NDP

• Intel Mobile Pentium 4 Processor 1.60GHz

– Processor core speed: 1.60GHz (Performance Mode at 1.30V) and

1.20GHz (Battery Optimized Mode at 1.20V)

– Processor bus speed: 400MHz

– Integrated L1 cache memory: 12KB instruction cache and 8KB write-

back data cache, 4-way set associative

– Integrated L2 cache memory: 512KB ECC protected cache data array,

8-way set associative

– Integrated NDP

Memory

Two BTO/CTO-compatible expansion memory slots are provided. Expansion up to

1024 MB is available.

• DDR-SDRAM (Double Data Rate - Synchronous DRAM @133MHz)

• 128 MB/256/512 MB selectable

− 128 MB (128Mbit 8M×16bit, 8P) or (16M×16bit, 4P)

− 256 MB (256Mbit 16M×16bit, 8P)

− 512 MB (512Mbit 32M×16bit, 8P) or (256Mbit 16M×16bit, 16P)

• 200 pin, SO Dual In-line Memory Modules. (SO-DIMM)

• 2.5 volt operation

• No parity bit

• Data transfer is 64-bit width

Loading...

Loading...