5Serial Ports

5 – 35

SCLK cycle, the serial port becomes active, looking for a frame sync.

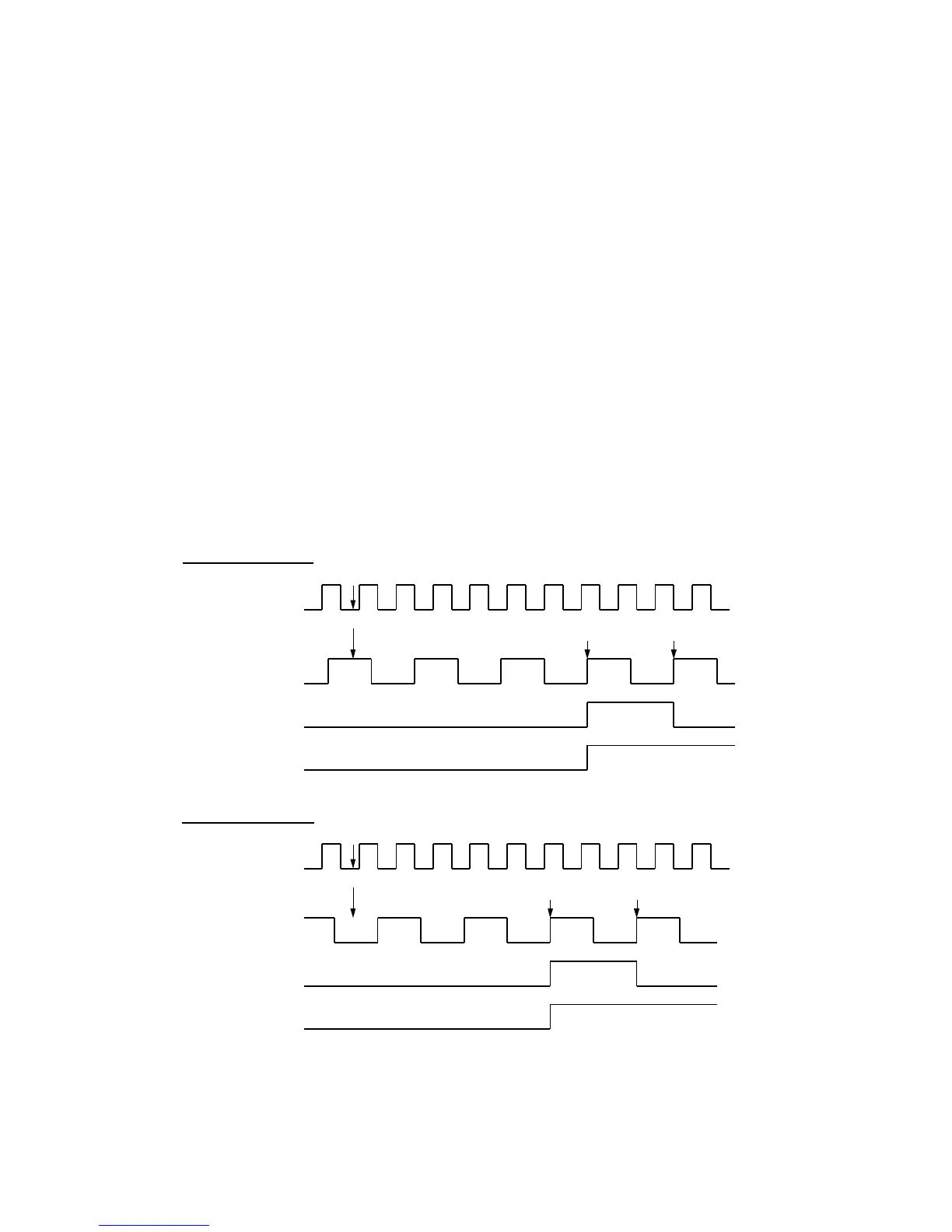

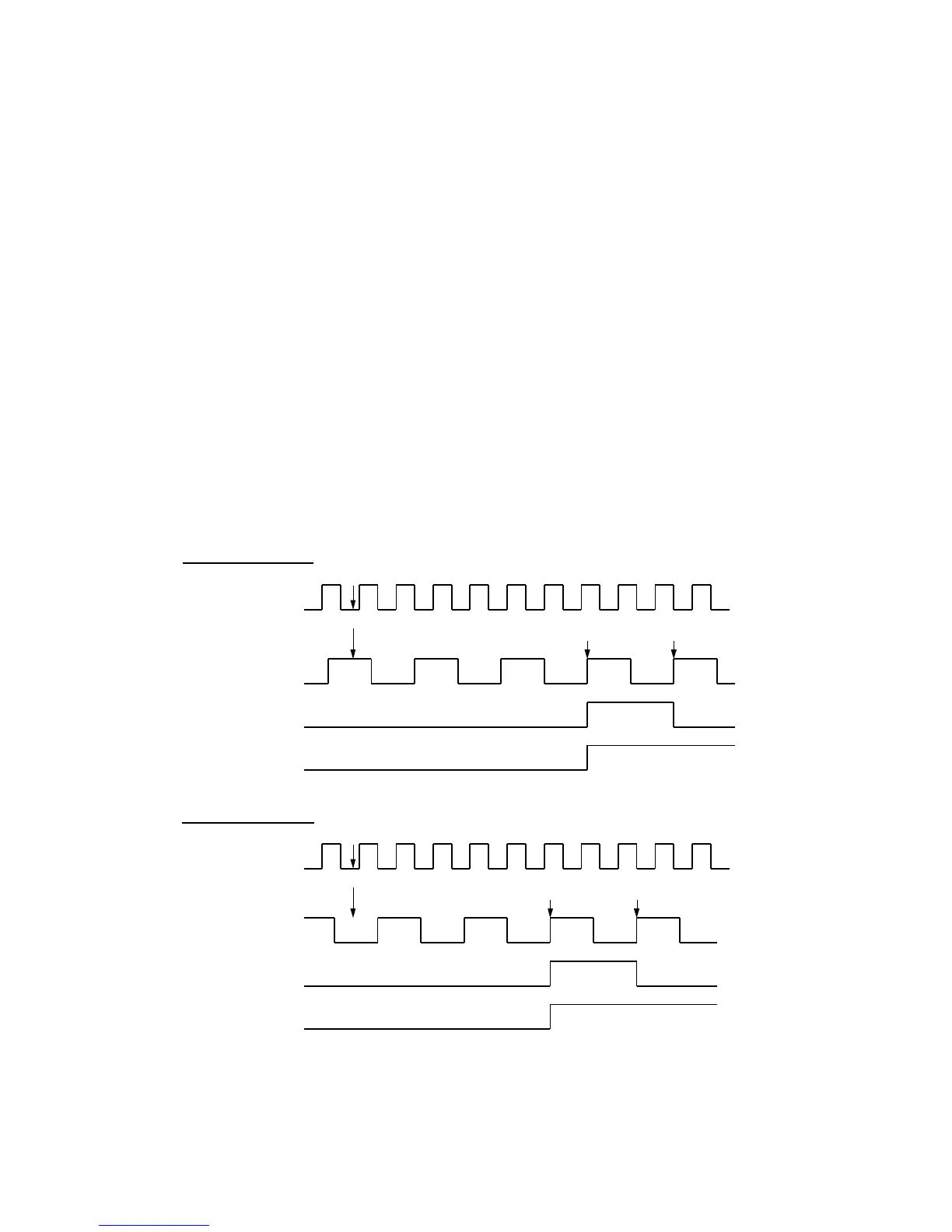

5.13.3 Internally Generarated Frame Sync Timing

When internally generated frame syncs are used, all that is necessary to

transmit data, from the programmer’s point of view, is to move the data

into the appropriate TX register with an instruction such as:

TX0 = AX0;

Once data is written into the TX register, the processor generates a frame

sync after a synchronization delay. This delay in turn affects the timing of

the serial port transmit interrupt. The latency depends on five factors: the

frequency of the serial clock, whether or not companding is enabled,

whether or not there is contention for the companding circuit, whether the

current word has finished transmitting and the logic level of the SCLK

Serial Clock

TX Written

Processor Clock

High Low High

MSB Transmitted

(Alternate Framing)

Serial Clock

Processor Clock

High

High

TX Written, SCLK High

TX Written, SCLK Low

TX Written

TFS OUTPUT

(Normal Framing)

TFS OUTPUT

(Alternate Framing)

TFS OUTPUT

(Normal Framing)

TFS OUTPUT

(Alternate Framing)

MSB Transmitted

(Normal Framing)

MSB Transmitted

(Alternate Framing)

MSB Transmitted

(Normal Framing)

Figure 5.30 Clock Synchronization

Loading...

Loading...