5Serial Ports

5 – 39

latencies exist for all external interrupts. The processor can only service

interrupt or autobuffer requests on instruction cycle boundaries, so there

may be additional latency cycles added due to the completion of an

instruction.

5.13.7 Instruction Completion Latencies

There are several situations which can cause an instruction to take more

than one processor cycle. Any of the following can delay the processor’s

ability to service a pending interrupt or autobuffer request:

• External memory wait states

• Bus request when an external access is required (in go-mode)

• Bus request with go-mode disabled

• Multiple external accesses required for a single instruction

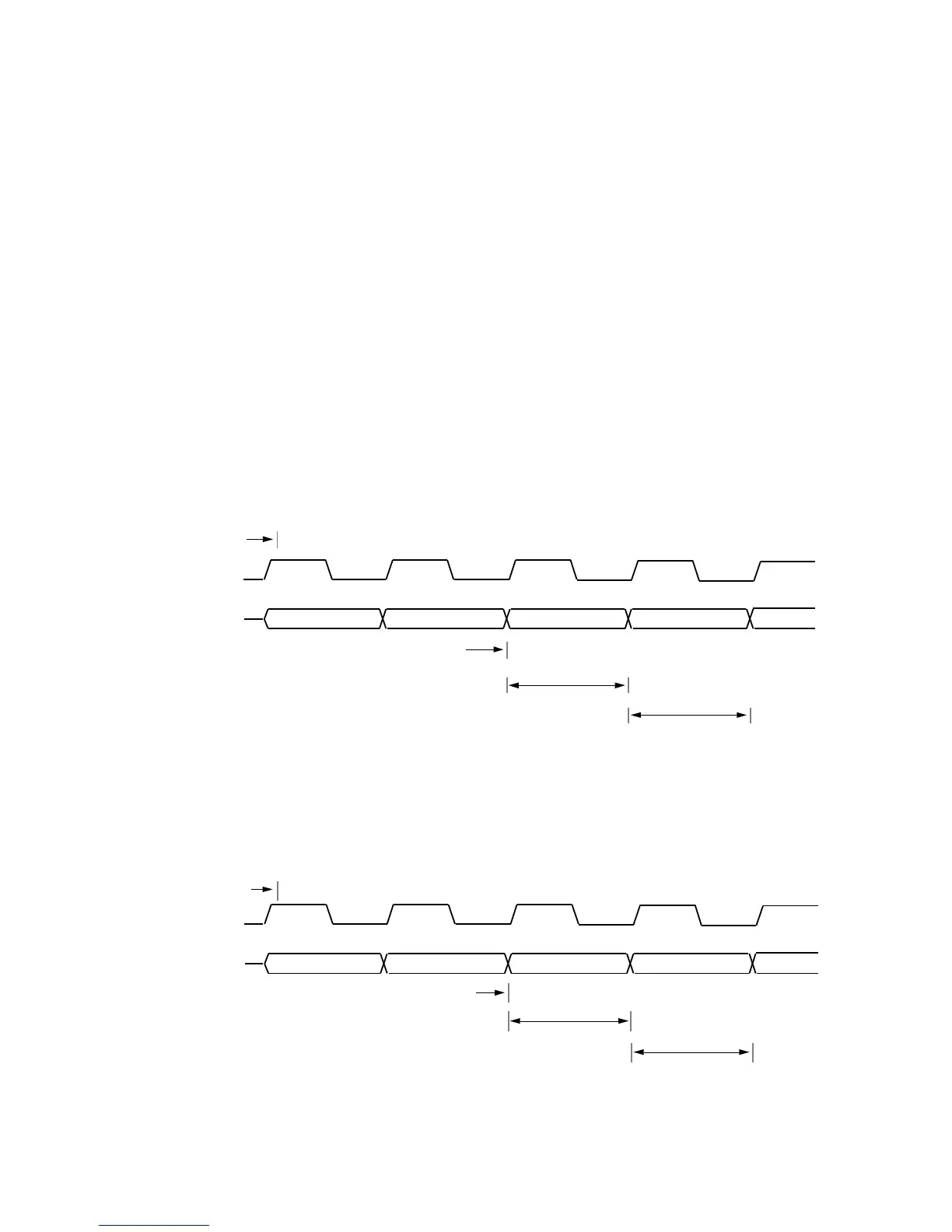

Request

CLKOUT

EXEC

A B FETCH INT INT

Sync Delay

NOP Instruction, Fetch Vector

Execute First Instruction Of Interrupt Routine

Figure 5.35 Interrupt Service Example

• A pending higher priority autobuffer or interrupt request

• Interrupt being masked

On instruction cycle boundaries the processor will service multiple pending

interrupt or autobuffer requests in the following priority order:

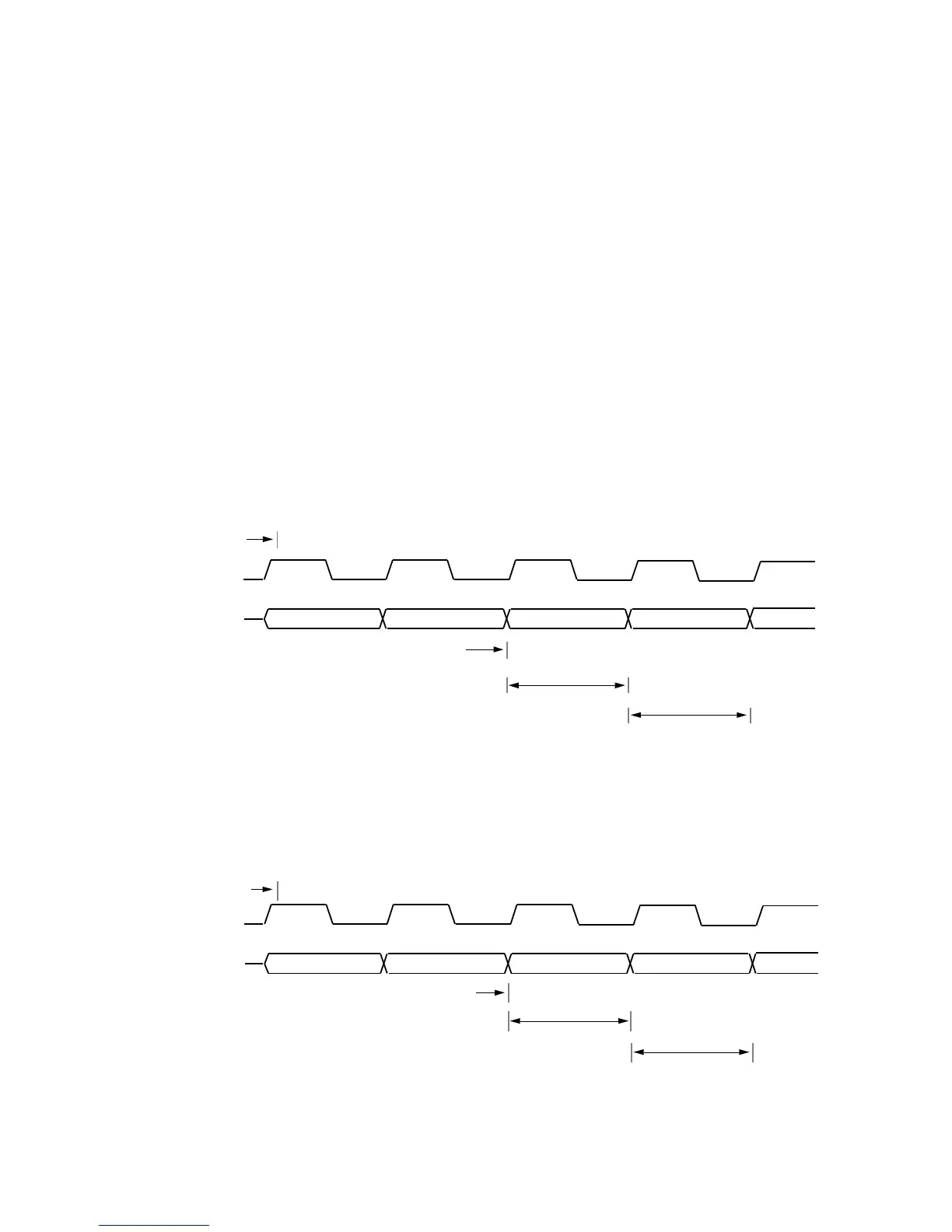

Figure 5.36 Autobuffer Service Example

Request

CLKOUT

EXEC

A B AUTOBUFFER C

Sync Delay

Do The Autobuffer Transfer

Continue Main Program

Loading...

Loading...