15

15 – 67

Syntax: reg = DM ( <addr> ) ;

Permissible registers

AX0 MX0 SI SB CNTR

AX1 MX1 SE PX OWRCNTR (write only)

AY0 MY0 SR1 ASTAT RX0

AY1 MY1 SR0 MSTAT RX1

AR MR2 I0-I7 TX0

MR1 M0-M7 IMASK TX1

MR0 L0-L7 ICNTL IFC(write only)

Example: SI = DM( ad_port0 );

Description: The Read instruction moves the contents of the data

memory location to the destination register. The addressing mode is direct

addressing (designated by an immediate address value or by a label). The

data memory address is stored directly in the instruction word as a full 14-

bit field. The contents of the source are always right-justified in the

destination register after the read (bit 0 maps to bit 0).

Note that whenever MR1 is loaded with data, it is sign-extended into

MR2.

Status Generated: None affected.

Instruction Format:

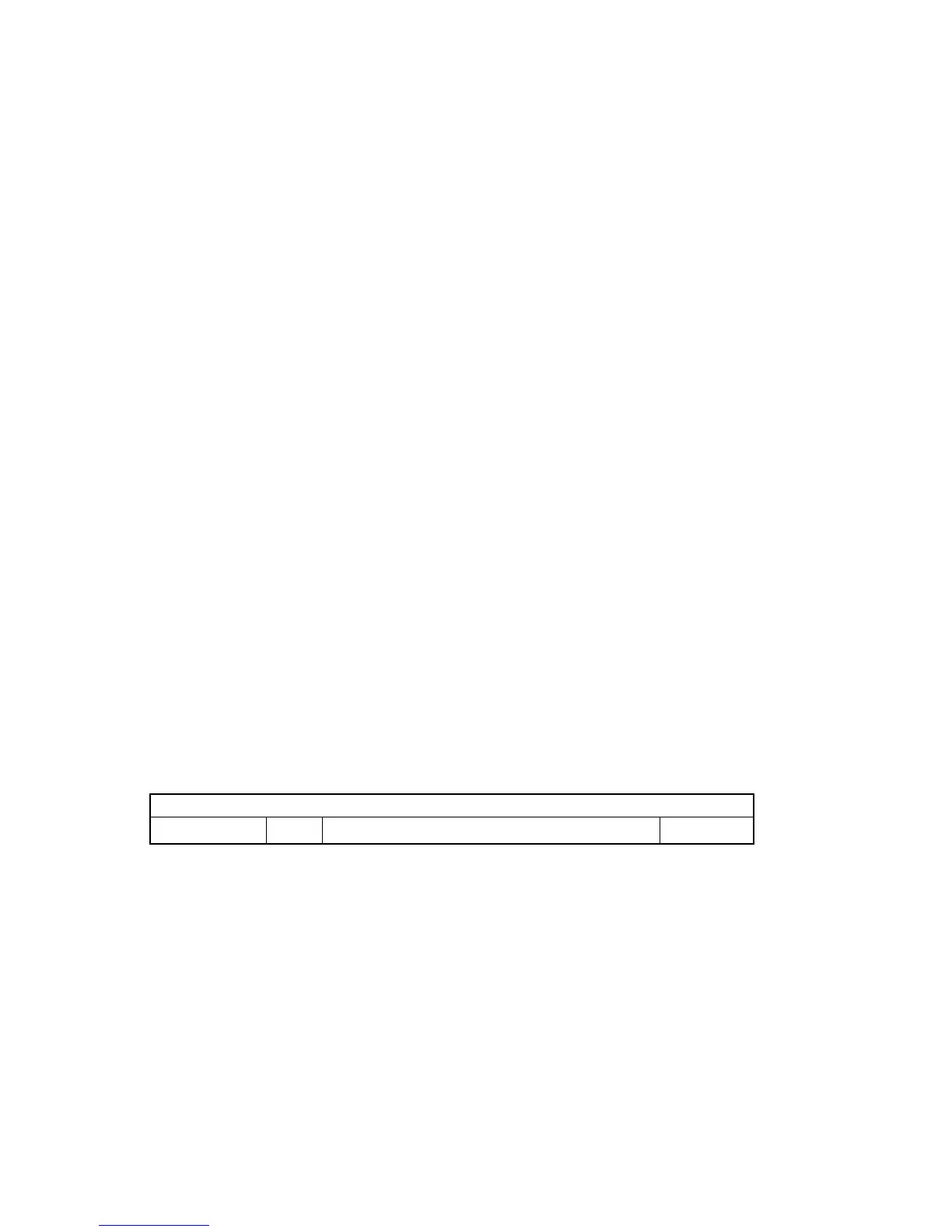

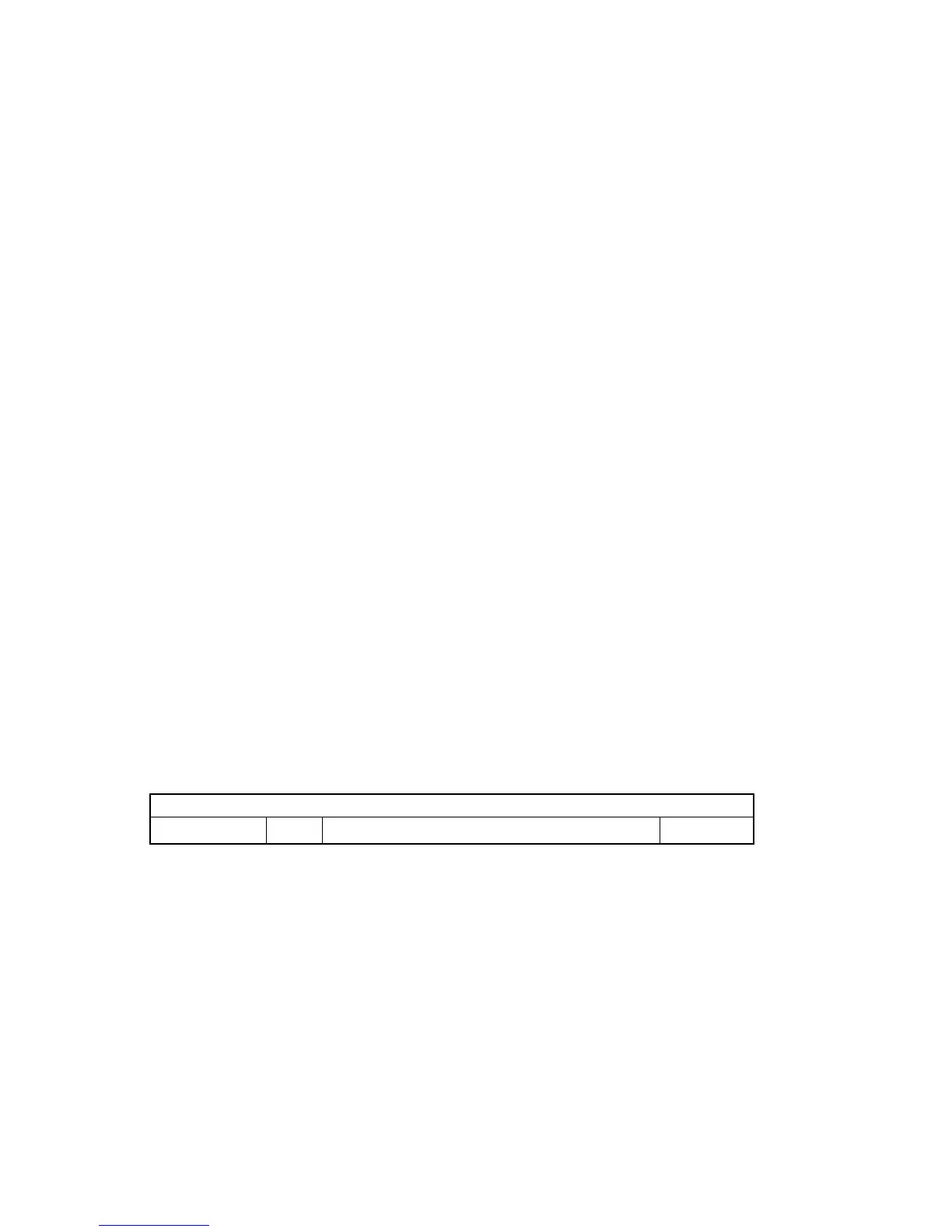

Data Memory Read (Direct Address), Instruction Type 3:

23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

1 0 0 0 RGP ADDR REG

ADDR contains the direct address to the source location in Data Memory.

RGP (Register Group) and REG (Register) select the destination register

according to the Register Selection Table (see Appendix A).

MOVE

DATA MEMORY READ (Direct Address)

Loading...

Loading...