Program Control3

3 – 20

3.5 STATUS REGISTERS & STATUS STACK

Processor status and mode bits are maintained in internal registers which

can be independently read and written over the DMD bus. These registers

are:

ASTAT Arithmetic status register

SSTAT Stack status register(read-only)

MSTAT Mode status register

ICNTL Interrupt control register

IMASK Interrupt mask register

IFC Interrupt force/clear register(write-only)

The interrupt-configuring status registers are described in the previous

section. ASTAT, SSTAT, and MSTAT are discussed in the following

sections.

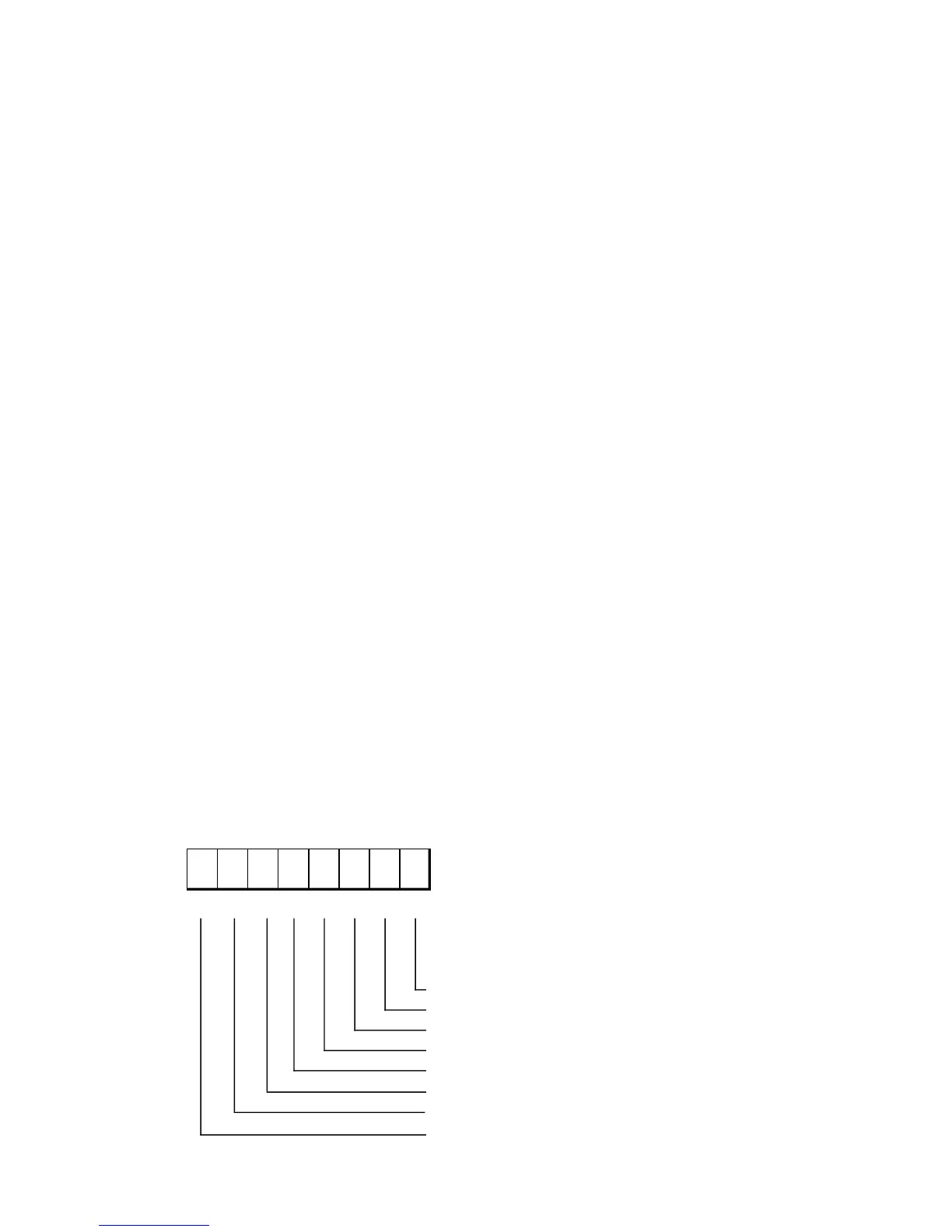

The current ASTAT, MSTAT, and IMASK values are pushed onto the

status stack when the processor responds to an interrupt; they are popped

upon return from the interrupt service routine (with the RTI instruction).

The depth of the stack varies from processor to processor. In each case,

sufficient stack depth is provided to accommodate nesting of all

interrupts.

3.5.1 Arithmetic Status Register (ASTAT)

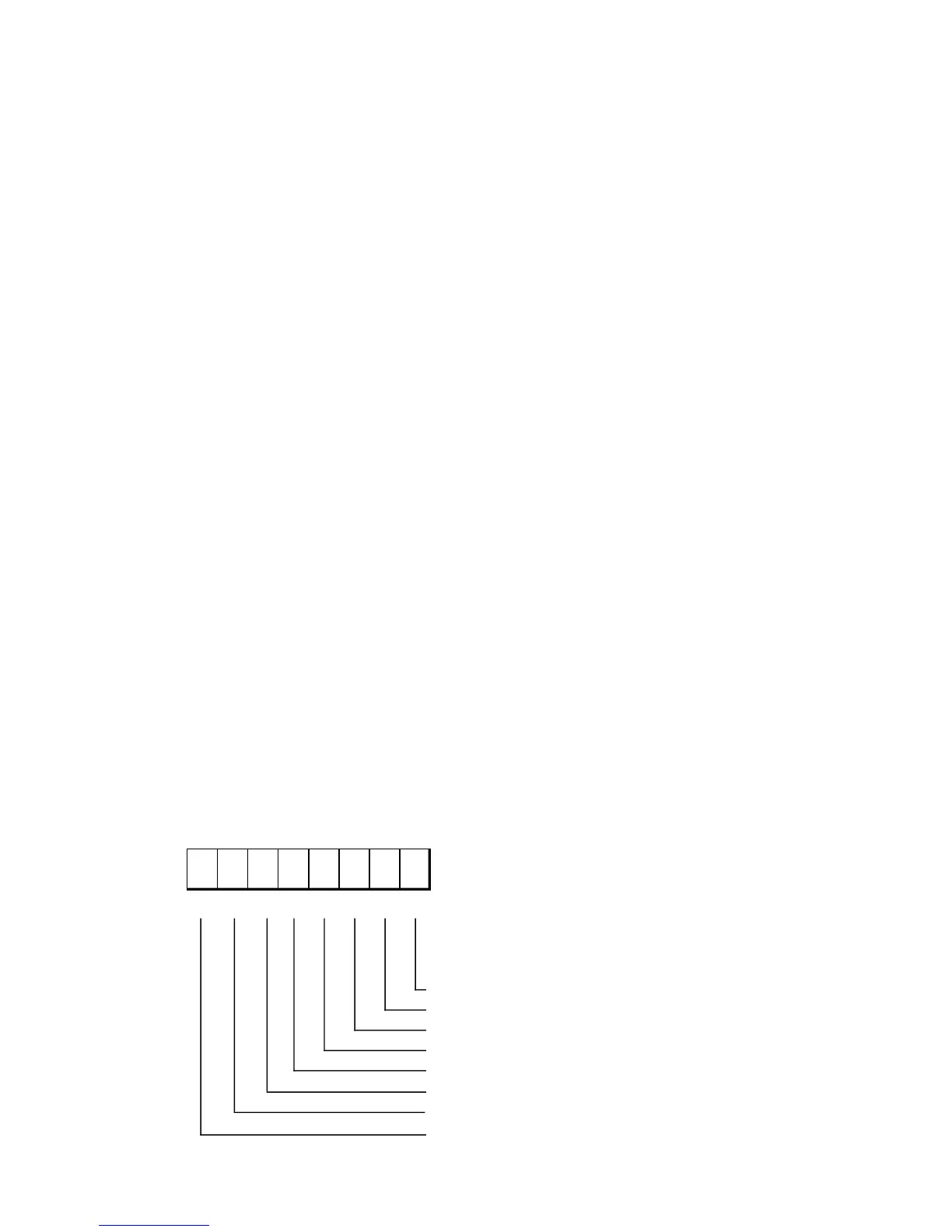

ASTAT is eight bits wide and holds the status information generated by

the computational blocks of the processor. The individual bits of ASTAT

are defined as shown in Figure 3.4. The bits which express a particular

condition (AZ, AN, AV, AC, MV) are all positive sense (1=true, 0=false).

543210

000000

76

00

ALU Result Zero

ALU Carry

ALU X Input Sign

ALU Result Negative

ALU Overflow

SS ASMV AQ AC ANAV AZ

ALU Quotient

MAC Overflow

Shifter Input Sign

Figure 3.4 ASTAT Register

Loading...

Loading...