11DMA Ports

11 – 23

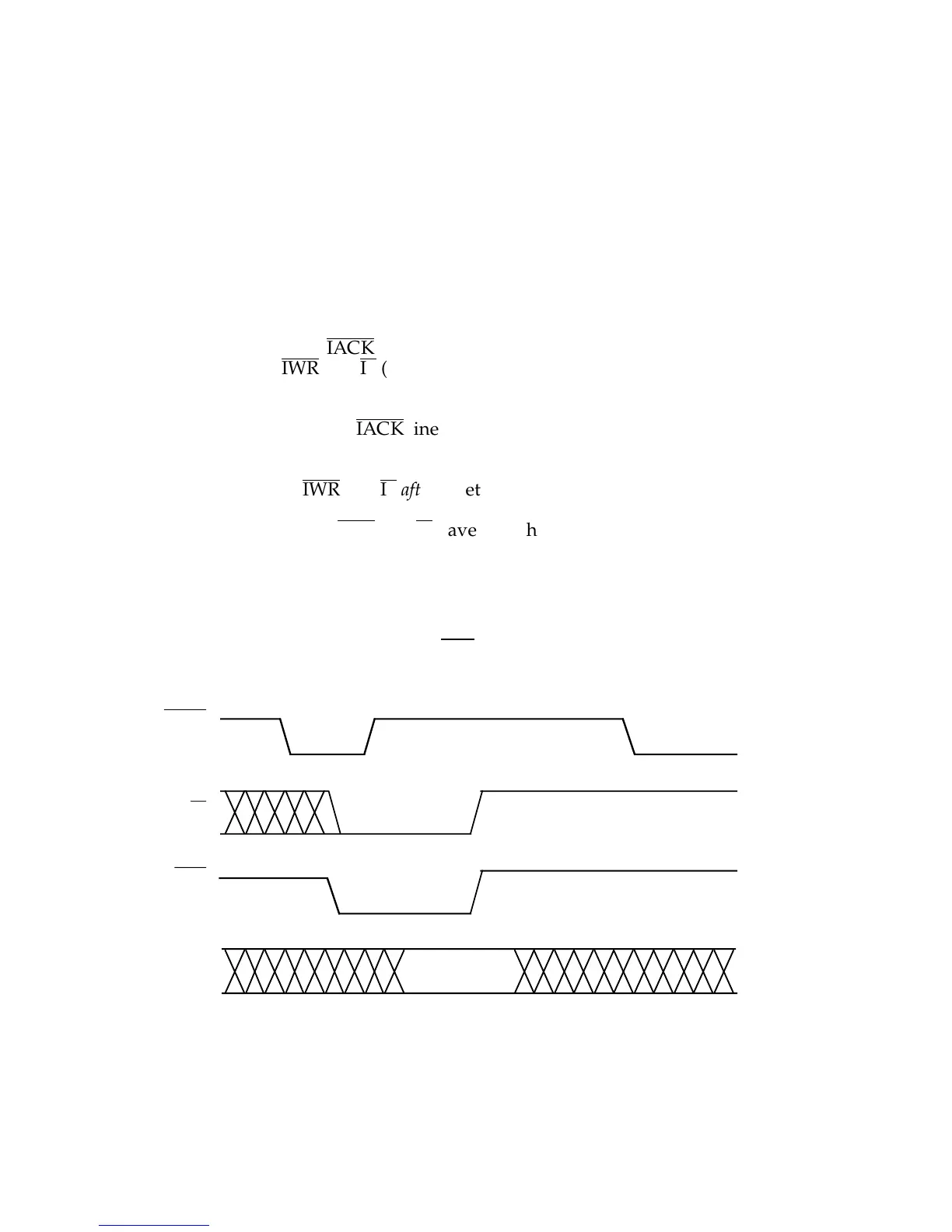

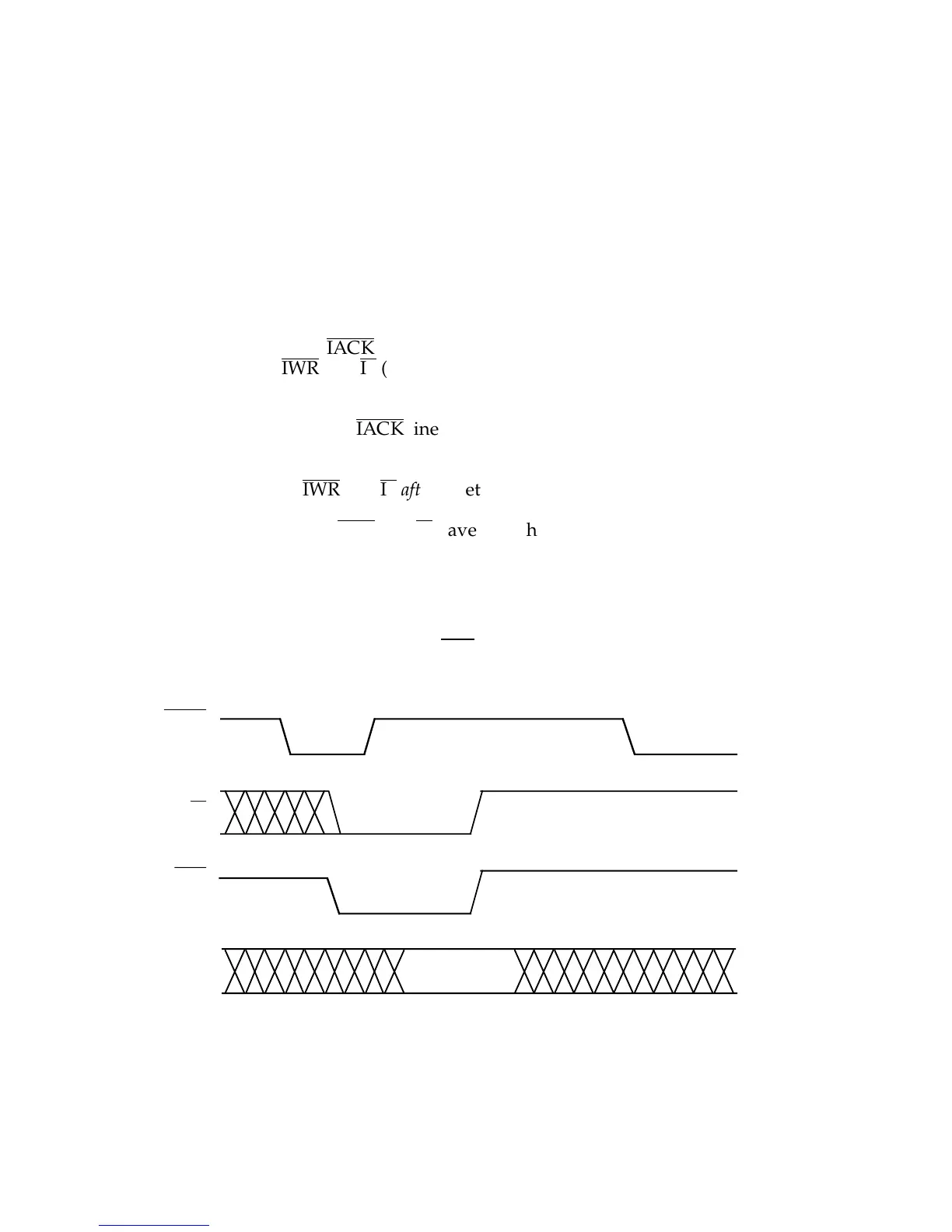

11.3.4.5 Short Write Cycle

The host writes the contents of a ADSP-2181 internal memory location using the

IDMA short write cycle. The write cycle, shown in Figure 11.13, consists of the

following steps:

1. Host ensures that

IACK

line is low.

2. Host asserts

IWR

and

IS

(low), directing the ADSP-2181 to write the data on

the IAD15-0 address/data bus to the location pointed to by the target IDMA

address .

3. ADSP-2181 deasserts

IACK

line (high), indicating it recognizes the IDMA

write operation.

4. Host drives the data on the IAD address/data bus.

5. Host deasserts

IWR

and

IS

after meeting the short write timing requirements

(ending the short write cycle).

6. ADSP-2181 detects

IWR

and

IS

have gone high, then latches the data on the

IAD address/data bus.

7. Host stops driving the data on the IAD15-0 address/data bus after meeting

the short write timing requirements.

Note that IAL is low (inactive) and

IRD is high (inactive) throughout the write

operation.

IACK

IS

IWR

IAD15-0

DATA

Figure 11.13 IDMA Short Write Cycle Timing

Loading...

Loading...