15

15 – 103

Syntax:

AX0 = DM ( I0 , M0 ) , AY0 = PM ( I4 , M4 ) ;

AX1 I1 M1 AY1 I5 M5

MX0 I2 M2 MY0 I6 M6

MX1 I3 M3 MY1 I7 M7

Description: Perform the designated memory reads, one from data

memory and one from program memory. Each read operation moves the

contents of the memory location to the destination register. For this double

data fetch, the destinations for data memory reads are the X registers in

the ALU and the MAC, and the destinations for program memory reads

are the Y registers. The addressing mode for this memory read is register

indirect with post-modify. For linear (i.e. non-circular) indirect

addressing, the L register corresponding to the I register used must be

set to zero. The contents of the source are always right-justified in the

destination register.

A multifunction instruction requires three items to be fetched from

memory: the instruction itself and two data words. No extra cycle is

needed to execute the instruction as long as only one of the fetches is from

external memory.

If two off-chip accesses are required, however—the instruction fetch and

one data fetch, for example, or data fetches from both program and data

memory—then one overhead cycle occurs. In this case the program

memory access occurs first, then the data memory access. If three off-chip

accesses are required—the instruction fetch as well as data fetches from

both program and data memory—then two overhead cycles occur.

Status Generated: No status bits are affected.

Instruction Format:

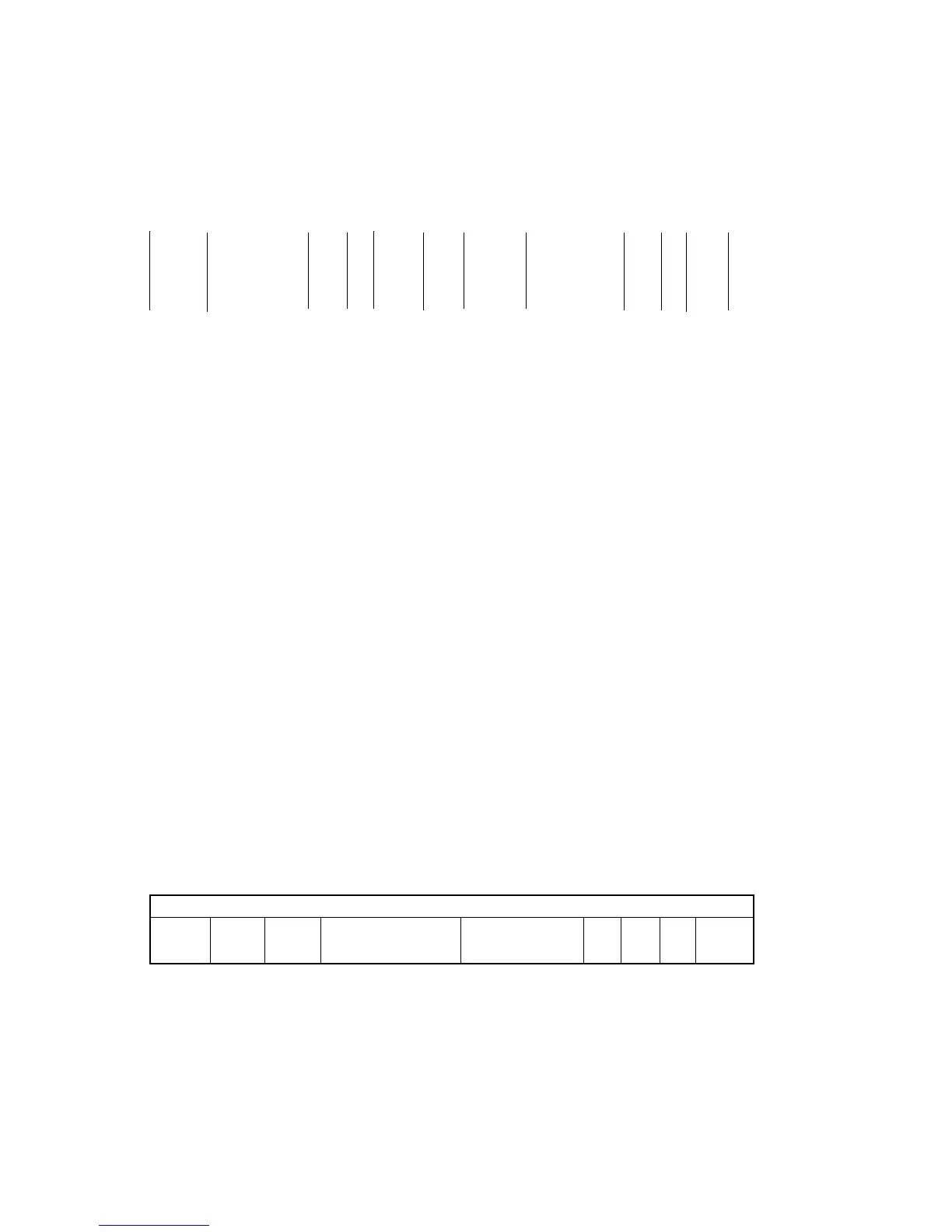

ALU/MAC with Data & Program Memory Read, Instruction Type 1:

23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

1 1 PD DD AMF 0 0 0 0 0 PM PM DM DM

I M I M

AMF specifies the ALU or MAC function. In this case, AMF = 00000,

designating a no-operation for the ALU or MAC function.

PD: Program Destination register DD: Data Destination register

AMF: ALU/MAC operation I: Indirect address register

M: Modify register

MULTIFUNCTION

DATA & PROGRAM MEMORY READ

Loading...

Loading...