15

15 – 102

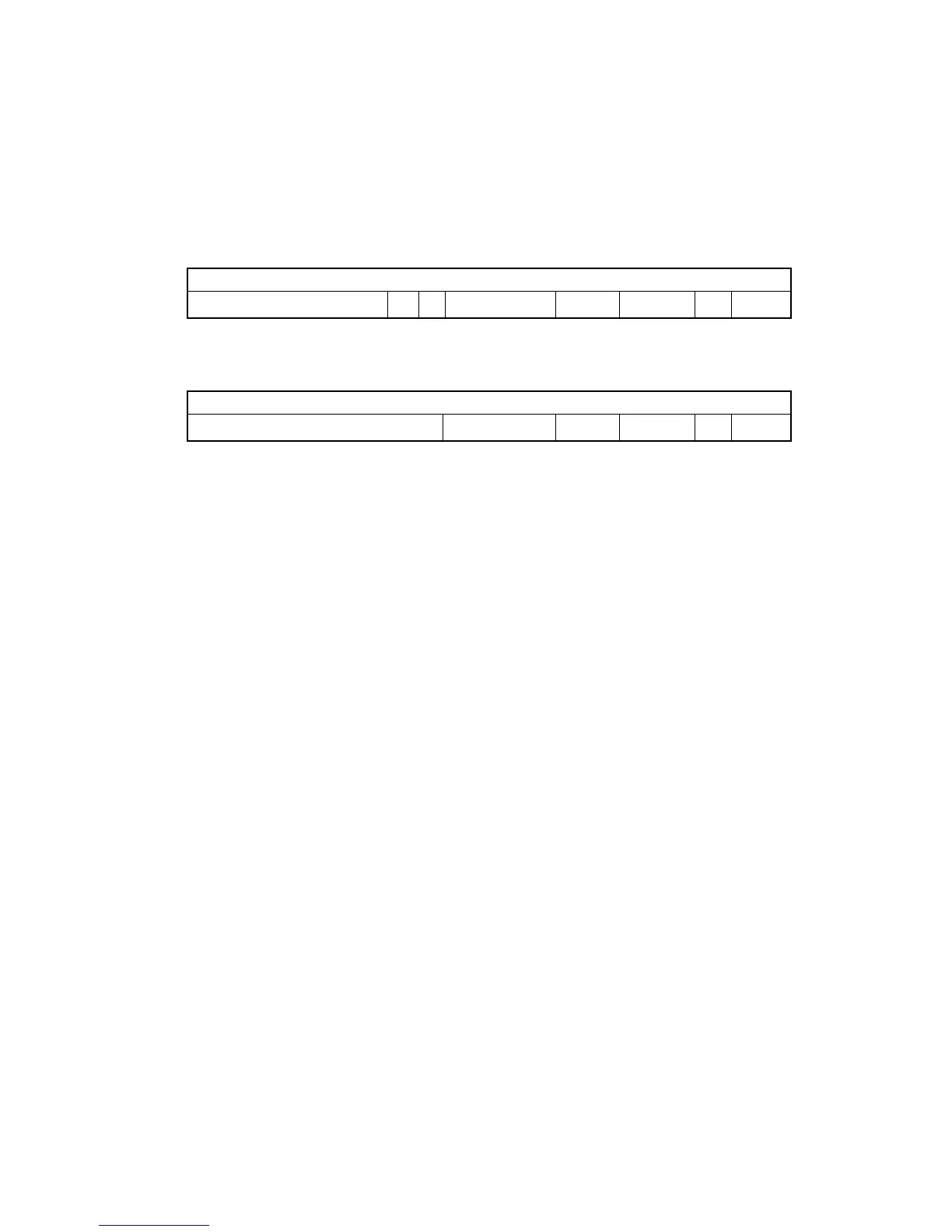

Shift operation with Data Memory Write, Instruction Type 12:

23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0 0 0 1 0 0 1 G 1 SF Xop Dreg I M

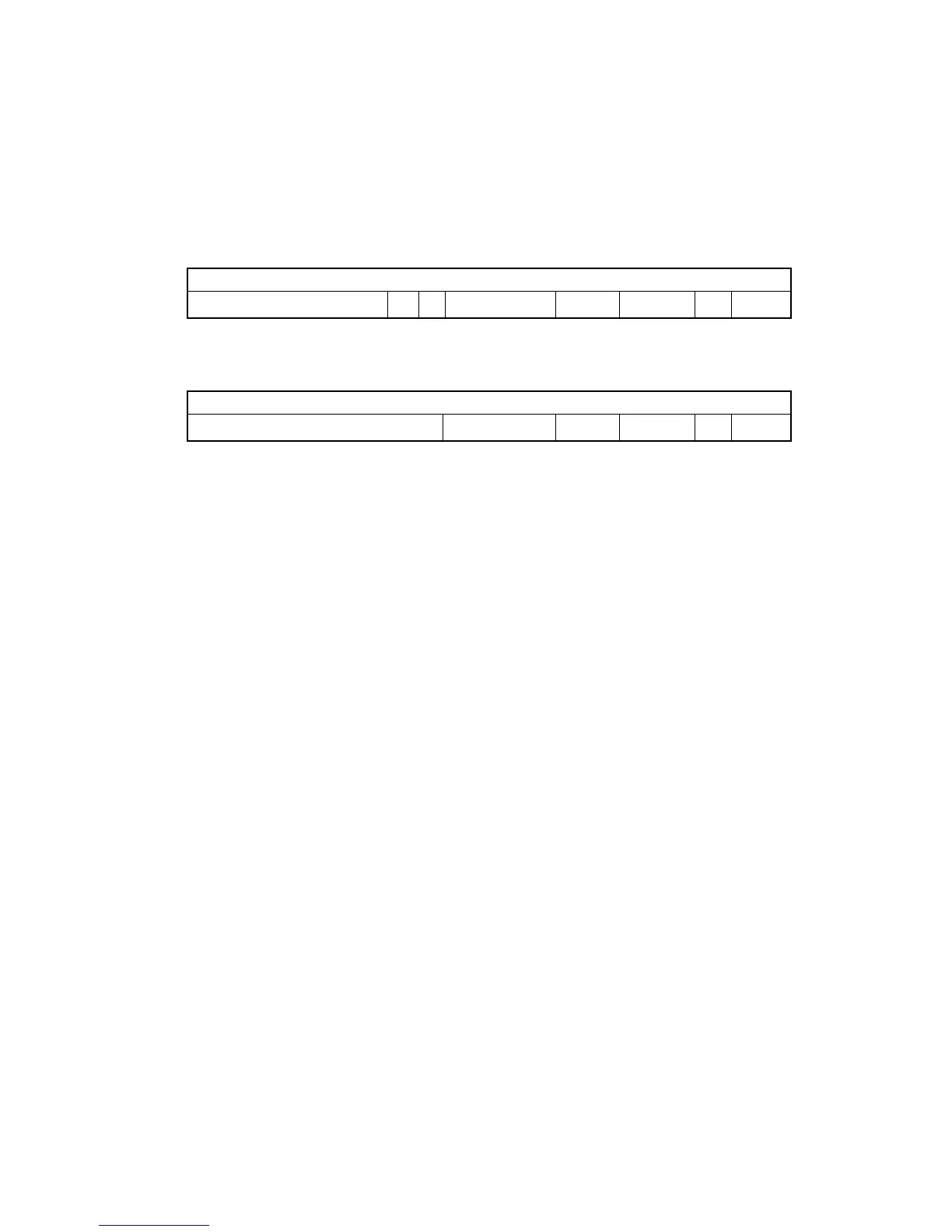

Shift operation with Program Memory Write, Instruction Type 13:

23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0 0 0 1 0 0 0 1 1 SF Xop Dreg I M

Z: Result register Dreg: Destination register

SF: Shifter operation AMF: ALU/MAC operation

Yop: Y operand Xop: X operand

I: Indirect address register M: Modify register

G: Data Address Generator;

I & M registers must be from

the same DAG, as separated

by the gray bar in the Syntax

description.

MULTIFUNCTION

COMPUTATION with MEMORY WRITE

Loading...

Loading...