3Program Control

3 – 19

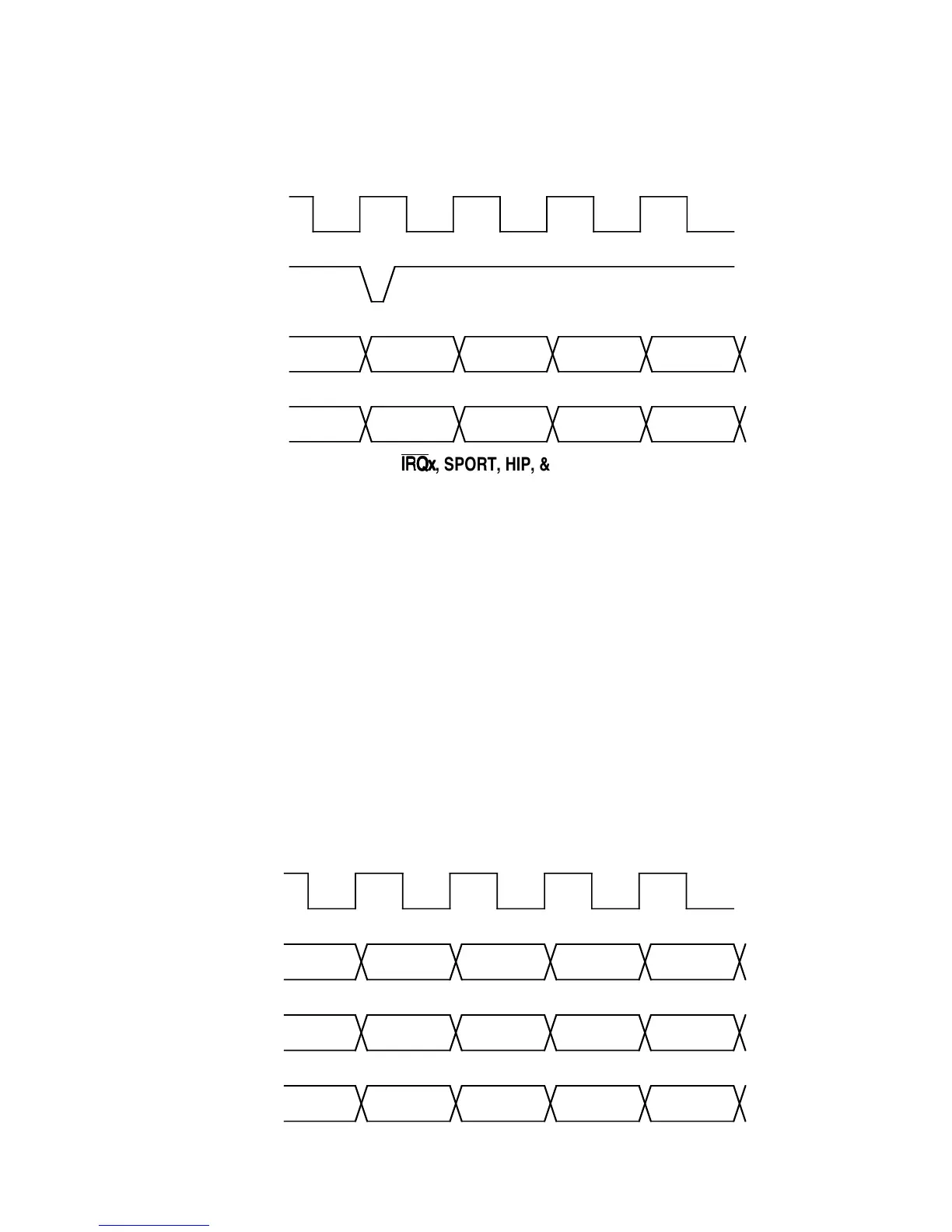

CLKOUT

Address for

Instruction Fetch

Interrupt

Instruction

Executing

n–2 n–1 n NOP

1st instr of

serv routine

n–1 n n+1

interrupt

vector i

i+1

Figure 3.2 Interrupt Latency (Timer,

IRQIRQ

IRQIRQ

IRQ

xx

xx

x

, SPORT, HIP, & Analog Interrupts)

(Note that this latency for the timer interrupt only applies for the ADSP-2171,

ADSP-2181, and ADSP-21msp58/59 processors. See the next section for a

description of timer interrupt latency on the ADSP-2101, ADSP-2105,

ADSP-2115, ADSP-2111.)

For a pending interrupt that is masked, the latency from execution of the

instruction that unmasks the interrupt (in IMASK) to the first instruction of

the service routine is one cycle. This one-cycle latency is similar to that shown

in Figure 3.3 for the timer interrupt of the ADSP-2101/2105/2111/2115, with

the “n” instruction executing being the instruction that writes to IMASK (to

unmask the interrupt).

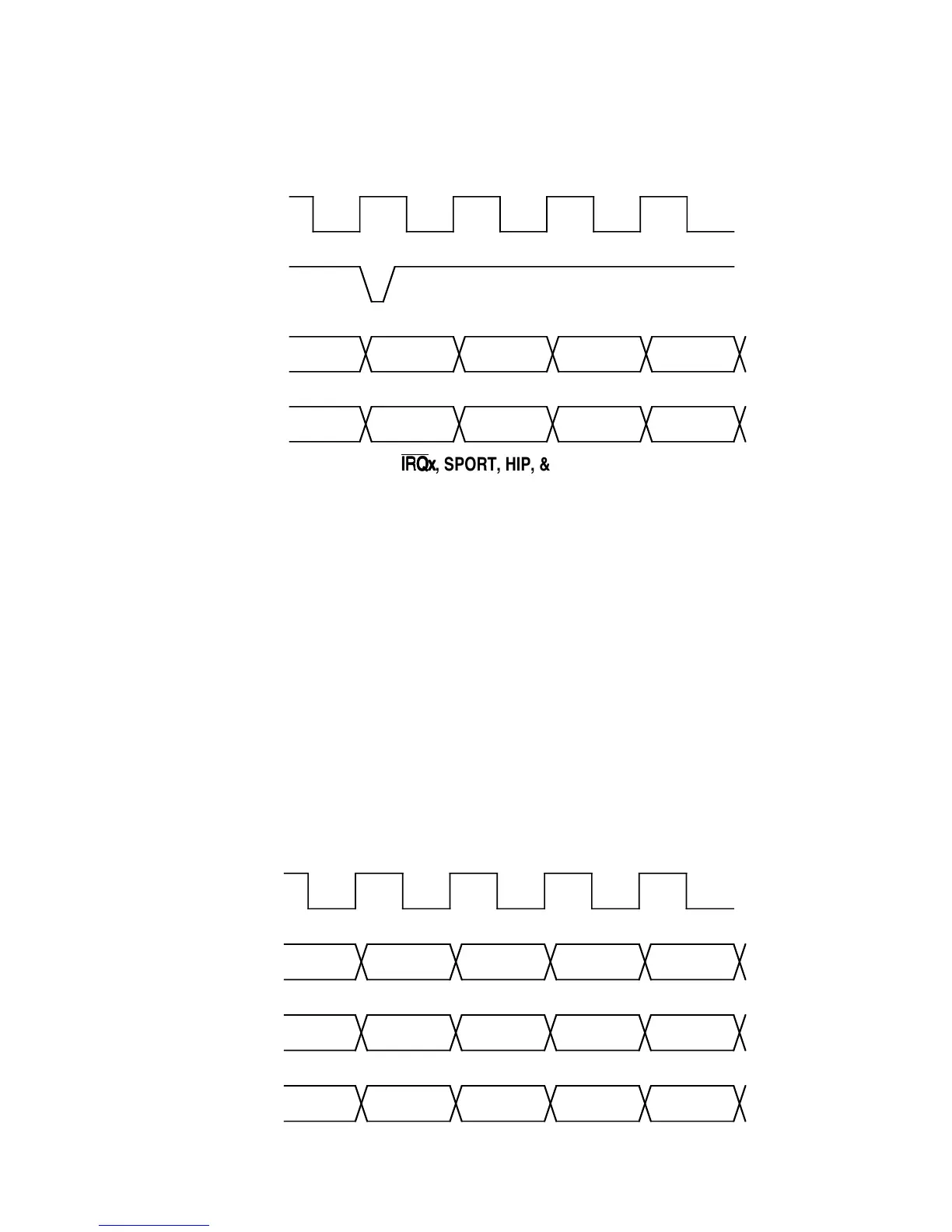

3.4.3.1 Timer Interrupt Latency on ADSP-2101, ADSP-2105, ADSP-2115, ADSP-2111

For the timer interrupt on these processors, the latency from when the

interrupt occurs to when the first instruction of the service routine is executed

is only one cycle. This is shown in Figure 3.3. The single cycle of latency is

needed to fetch the instruction stored at the interrupt vector location.

CLKIN

Address for

Instruction Fetch

Instruction

Executing

n+1

interrupt

vector i

i+1

n NOP

1st instr of

serv routine

Timer

Value

tcount=1 tcount=0

Figure 3.3 Timer Interrupt Latency for ADSP-2101, ADSP-2105, ADSP-2115, ADSP-2111

Loading...

Loading...