7Host Interface Port

7 –

3

H

SEL is a host select which allows the host to enable or disable the HIP for

host data transfers.

HACK is a host acknowledge output for hosts that require an acknowledge

for handshaking.

HSIZE configures the bus size; the HIP can function in both 8-bit and 16-

bit modes. If the HIP is configured for an 8-bit host (HSIZE=1), data is

read from and written to the lower eight bits of a HIP data register and the

upper eight bits are zero-filled (on host writes) or tristated (on host reads).

BMODE determines whether booting occurs through the HIP or through

the memory interface pins.

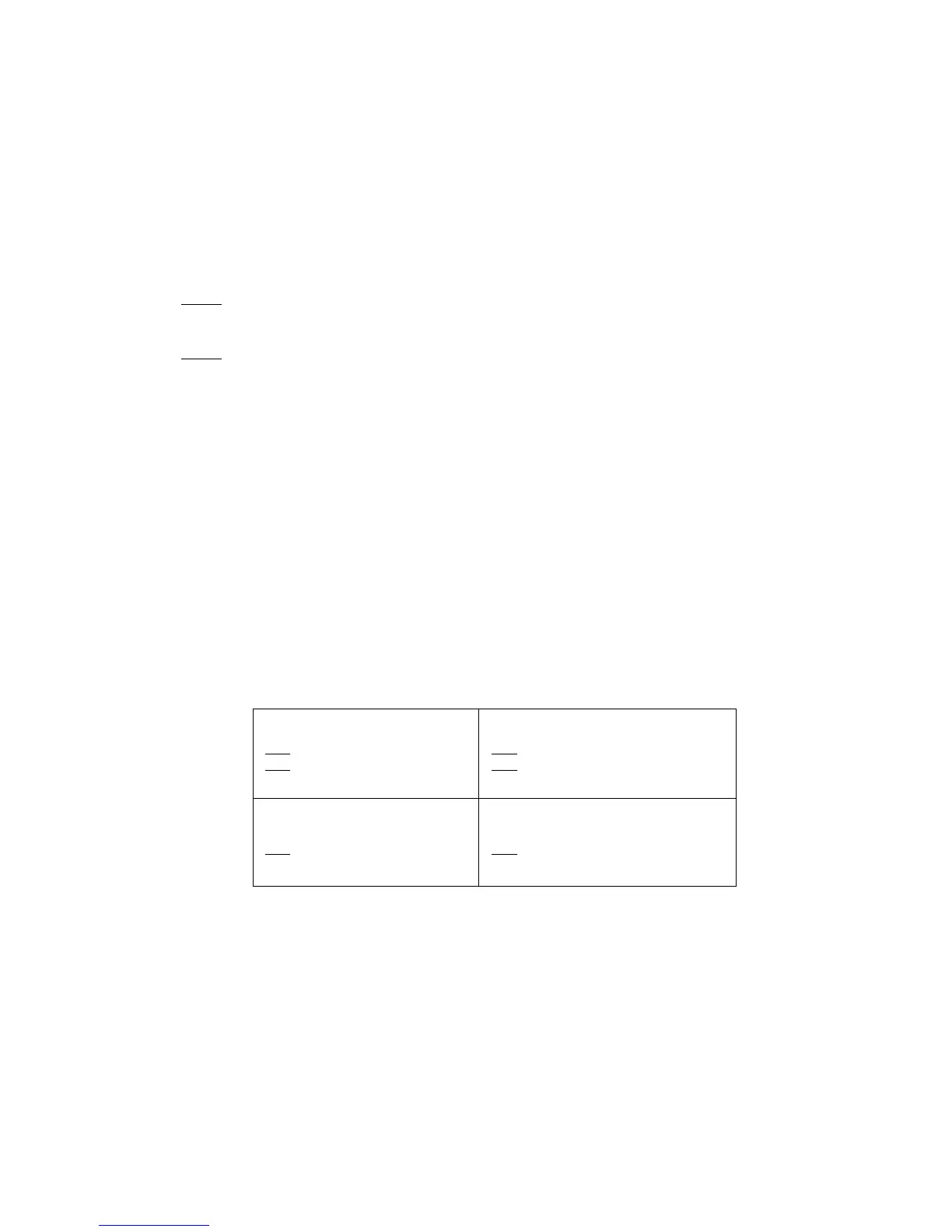

HMD0 and HMD1 are mode pins that configure the address, data and

strobe pins, as shown in Table 7.2. HMD0 configures the bus strobes,

selecting either separate read and write strobes or a single read/write

select and a host data strobe. HMD1 configures the bus protocol, selecting

either separate address (3-bit) and data (16-bit) buses or a multiplexed 16-

bit address/data bus with address latch enable. The timings of each of the

four bus protocols are described later in this chapter.

HMD1=0 HMD1=1

H

RD HIP Read Strobe HRD HIP Read Strobe

HMD0=0 HWR HIP Write Strobe HWR HIP Write Strobe

HD15-0 HIP Data HAD15-0 HIP Address/Data

HA2-0 HIP Address ALE HIP Address Latch Enable

HRW HIP Read/Write Select HRW HIP Read/Write Select

HMD0=1 HDS HIP Data Strobe HDS HIP Data Strobe

HD15-0 HIP Data HAD15-0 HIP Address/Data

HA2-0 HIP Address ALE HIP Address Latch Enable

Table 7.2 HIP Configuration Modes

Loading...

Loading...