GR740-UM-DS, Nov 2017, Version 1.7 220 www.cobham.com/gaisler

GR740

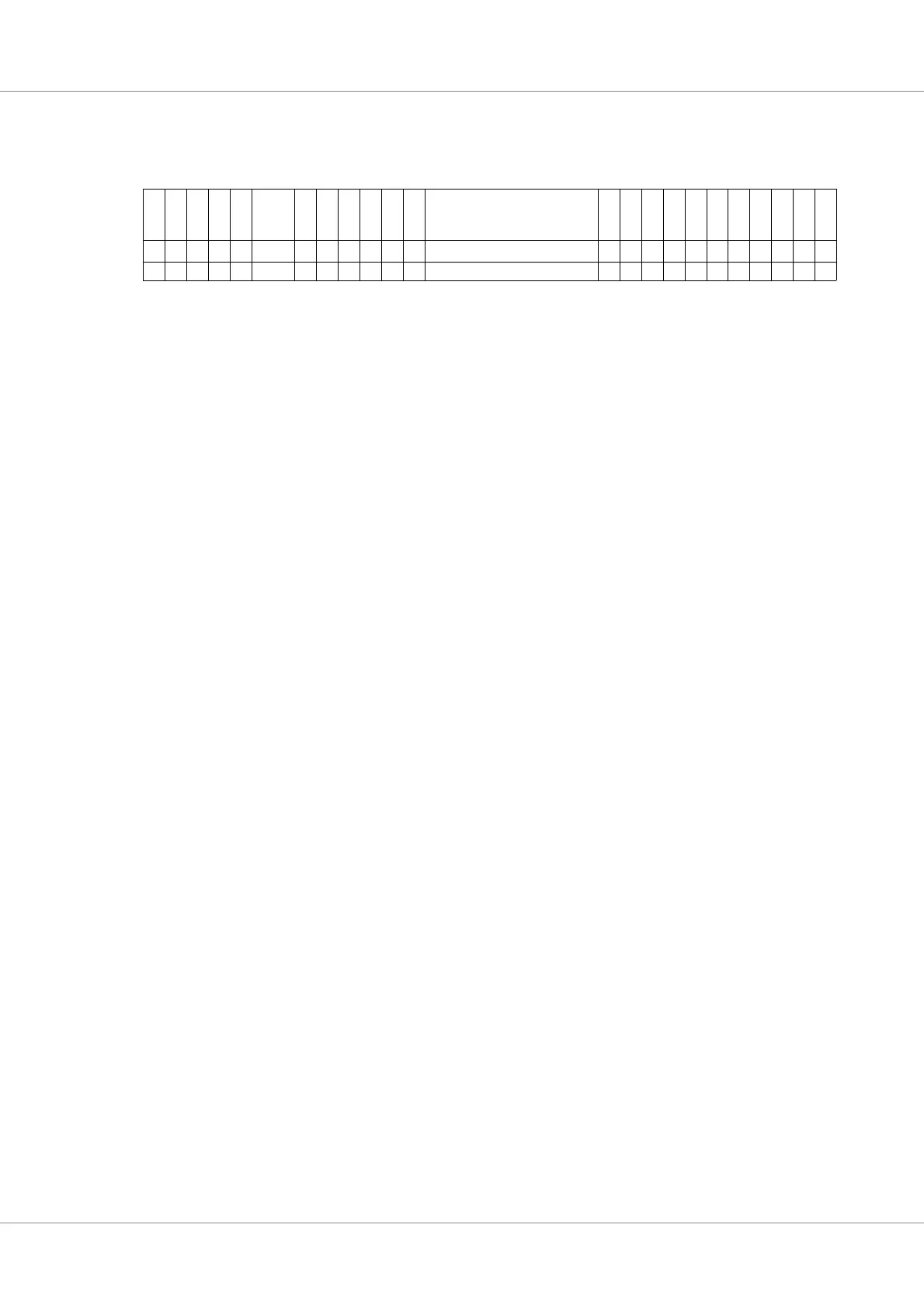

Table 250.0x04 - Status and Command register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 11 10 9 8 7 6 5 4 3 2 1 0

D

P

E

S

S

E

R

M

A

R

T

A

S

T

A

DEV

SEL

timing

M

D

P

E

F

B

B

C

R

E

S

66

M

H

z

CL IS RESERVED ID Not

Imp

SE Not

Imp

P

E

R

Not

Imp

M

W

I

Not

Imp

BM MS Not

Imp

0

0000 0b01 000*10 0 00000000000

wc wc wc wc wc r r r r r r r r rw r rw r rw r rw r rw rw r

31 Detected Parity Error (DPE)

30 Signaled System Error (SSE)

29 Received Master Abort (RMA)

28 Received Target Abort (RTA)

27 Signaled Target Abort (STA)

26: 25 DEVSEL timing - Returns “01“ indicating medium

24 Master Data Parity Error (MDPE)

23 Fast Back-to-Back Capable (FBBC) - Returns zero.

22 RESERVED

21 66 MHz Capable (66MHZ)

NOTE: In this implementation this bit has been defined as the status of the PCI_M66EN signal

rather than the capability of the core. For a 33 MHz design, this signal should be connected to

ground and this status bit will have the correct value of ‘0’. For a 66 MHz design, this signal is

pulled-up by the backplane and this status bit will have the correct value of ‘1’. For a 66 MHz capa-

ble design inserted in a 33 MHz system, this bit will then indicate a 33 MHz capable device.

20 Capabilities List (CL) - Returns one

19 Interrupt Status (IS)

18: 11 RESERVED

10 Interrupt Disable (DI)

9 NOT IMPLEMENTED, Returns zero.

8 SERR# Enable (SE)

7 NOT IMPLEMENTED, Returns zero.

6 Parity Error Response (PER)

5 NOT IMPLEMENTED, Returns zero.

4 Memory Write and Invalidate Enable (MWI)

3 NOT IMPLEMENTED, Returns zero.

2 Bus Master (BM)

1 Memory Space (MS)

0 NOT IMPLEMENTED, Returns zero.

Loading...

Loading...