GR740-UM-DS, Nov 2017, Version 1.7 321 www.cobham.com/gaisler

GR740

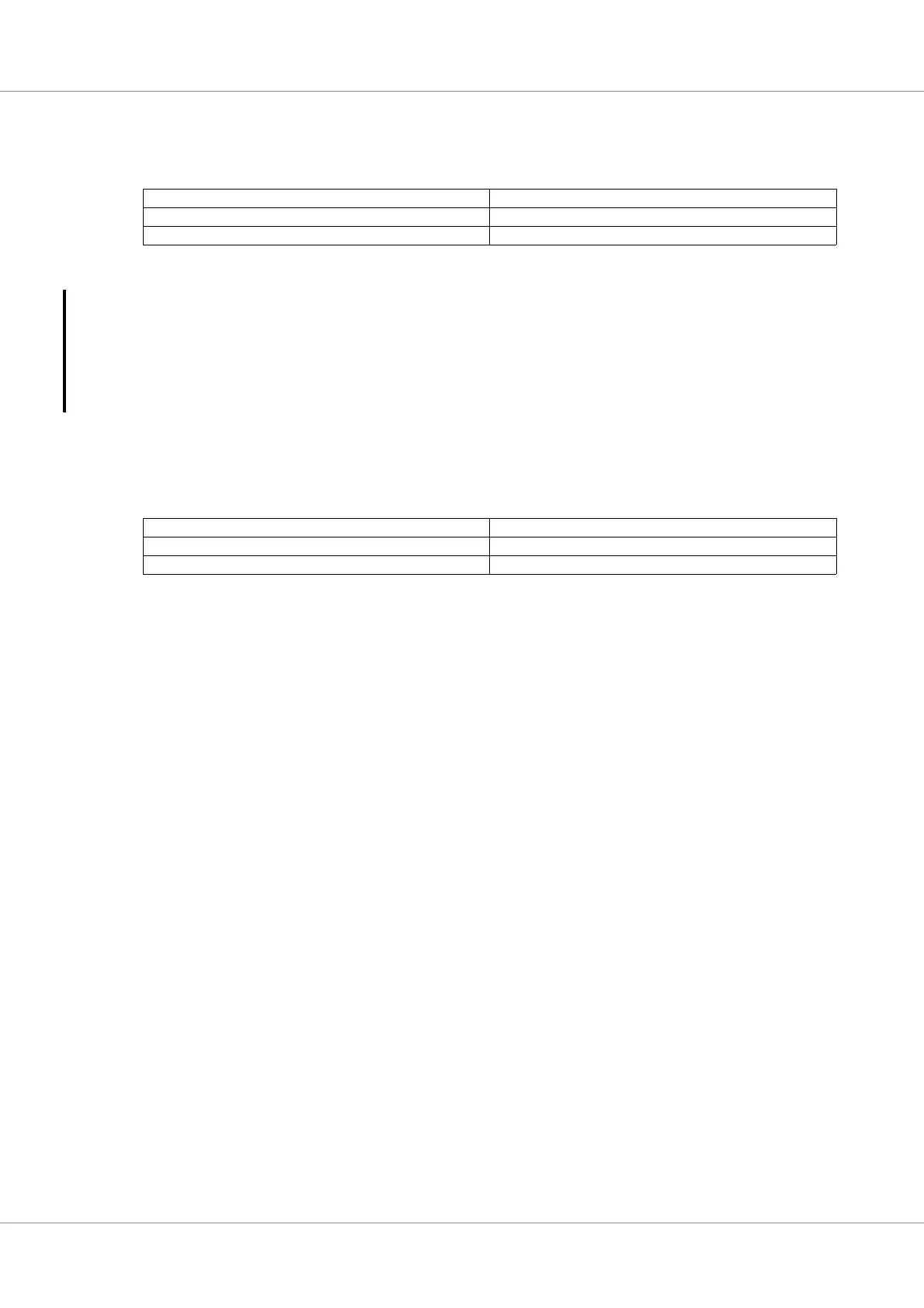

22.3.10 Interrupt flag register

Table 410.0x44 - IFLAG - Interrupt flag register

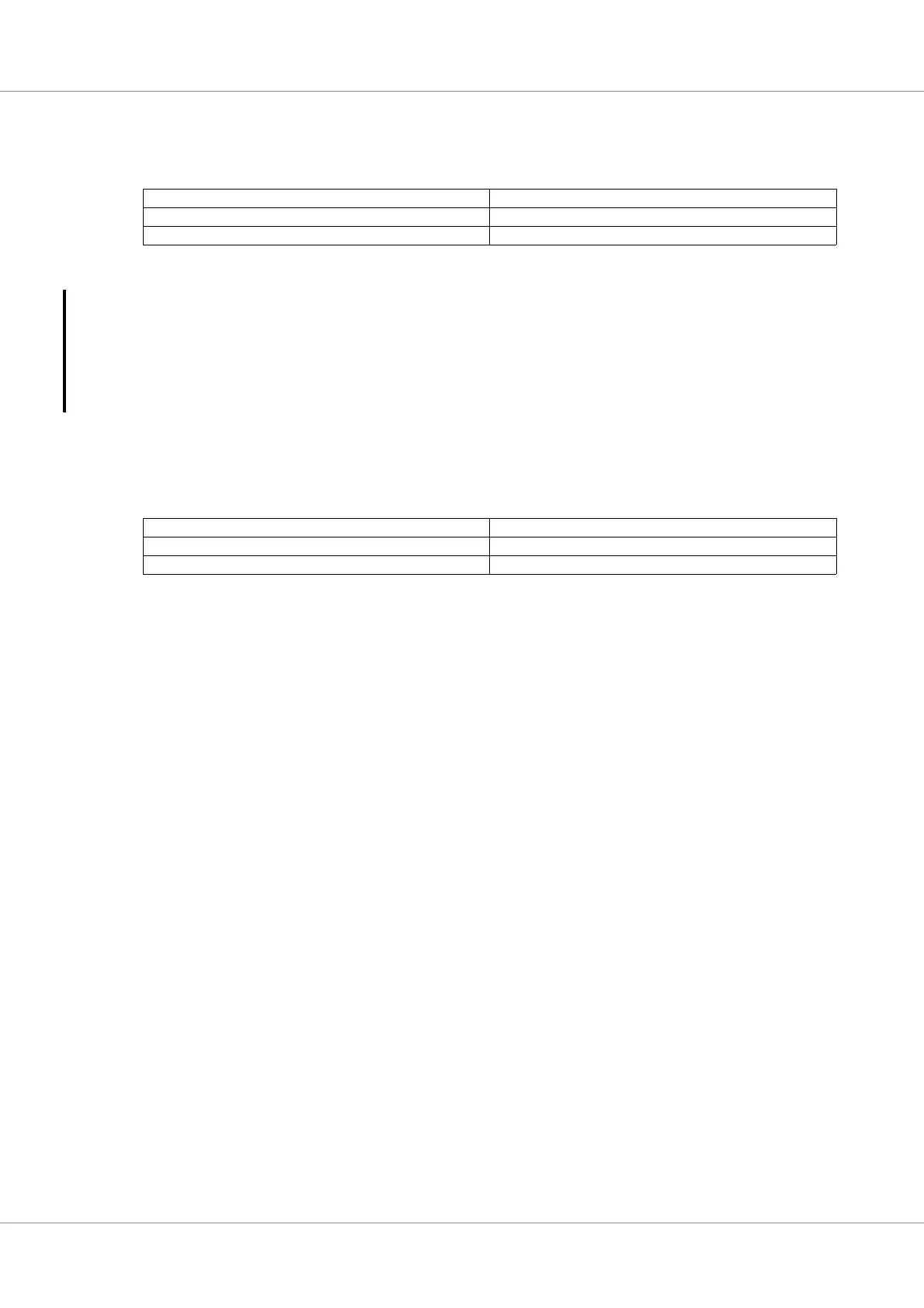

22.3.11 Pulse register

Table 411.0x4C - PULSE - Pulse register

31 16 15 0

RESERVED IFLAG

00

rwc*

31: 16 RESERVED

15: 0 IFLAG : If IFLAG[n] is set to ‘1’ then GPIO line n has generated an interrupt. The bit will be set

until cleared by writing ’1’ to the corresponding bit position.

Note that for GR740 silicon revision 0, the IFLAG register bit(s) will only be set while the inter-

rupt(s) is asserted. In silicon revision 0 this register is only practically usable when using level inter-

rupts. For edge interrupts, an IFLAG register bit will only be asserted during one cycle per interrupt

assertion. For silicon revision 1 the IFLAG register bits are be sticky bits that are set to one when an

interrupt has been generated and remain set until cleared by writing to this register.

31 16 15 0

RESERVED PULSE

00

rrw

31: 16 RESERVED

15: 0 PULSE : If PULSE[n] is set to ‘1’ then OUTPUT register bit n will be inverted on the following

events:

Position 0: GPTIMER 0 tick 0

Position 1: GPTIMER 0 tick 1

Position 2: GPTIMER 0 tick 2

Position 3: GPTIMER 0 tick 3

Position 4: GPTIMER 0 tick 4

Position 5: GRSPWTDP CTICK -A pulse is generated when SpaceWire Time-Code is transmitted

when TDP controller is acting as initiator. A pulse is also generated when a diagnostic SpaceWire

Time-Code is generated when TDP controller is acting as target.

Position 6: GRSPWTDP JTICK - The incoming SpaceWire Time-Code provides an output pulse

when the TDP controller is acting as target, this output is used to visualize the jitter in incoming

SpaceWire Time-Codes

Position 7 to 10: GRSPWTDP external datation pulse 0 to 3

Position 11 to 15: GPTIMER latch disabled for timer units 0 to 4.

This register is only available for the first GPIO port, GRGPIO 0.

See also section 5.9.

Loading...

Loading...