WSB-9152 PICMG 1.0 SBC

Page 17

Spatial Dithering support to emulate up to 16 million colors for 18bpp TFT

panels

Spread spectrum clocking (SSC) supported

o Supports down and center SSC via an SSC clock from an external SSC

clock chip.

o Supports down spread of – 2.5% or center spread of ± -1.25% in

reference 30-50 KHz modulation rate

SSC must be disabled for LVDS port and CRT DAC single pipe simultaneous

display mode.

Panel Power Sequencing support

o Power down state can be either zero volt or high impedance

Integrated PWM interface for LCD Backlight Inverter Control

Up to UXGA monitors with a maximum resolution of 1600 x 1200

18-bit 25 MHz to 112 MHz single-channel or dual-channel LVDS screens

CPIS 1.5 compliant LVDS screens

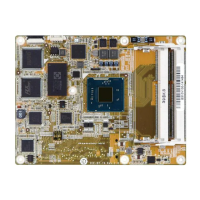

2.5.2.3 Chrontel 7307C

The Chrontel 7307C is pictured below.

Figure 2-8: DVI Controller

The Chrontel 7307C has the following features:

Maximum resolution: UXGA (1600x1200)

Bandwidth: 25 MHz – 165 MHz