If the data section has been updated, a transmission is requested by an Add Request via

TXBAR[ARn]. The requested messages arbitrate internally with messages from an

optional Tx FIFO or Tx Queue and externally with messages on the CAN bus, and are

sent out according to their Message ID.

A Dedicated Tx Buffer allocates Element Size 32-bit words in the Message RAM (see the

following table). Therefore the start address of a Dedicated Tx Buffer in the Message

RAM is calculated by adding transmit buffer index (0…31) x Element Size to the Tx

Buffer Start Address TXBC[TBSA].

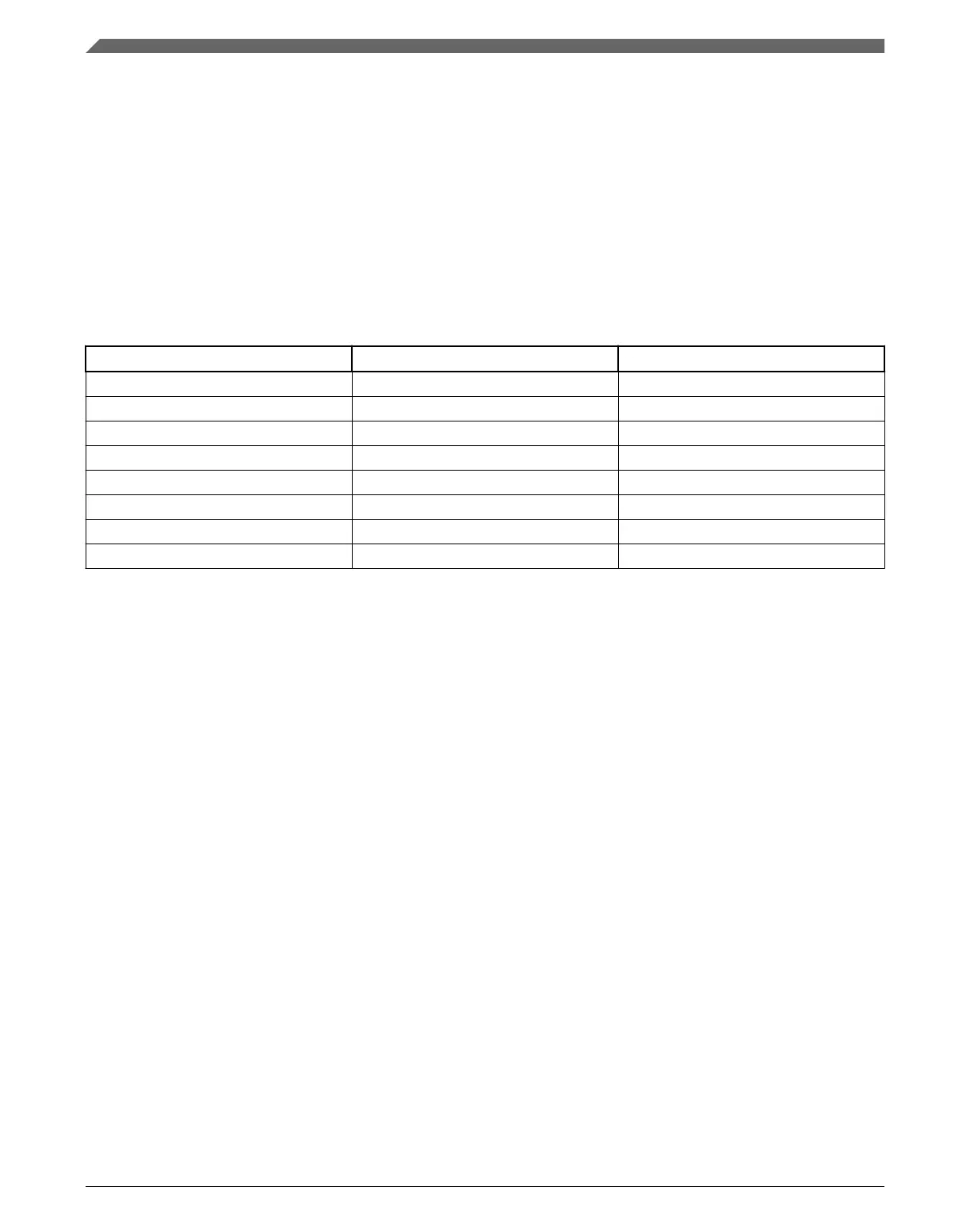

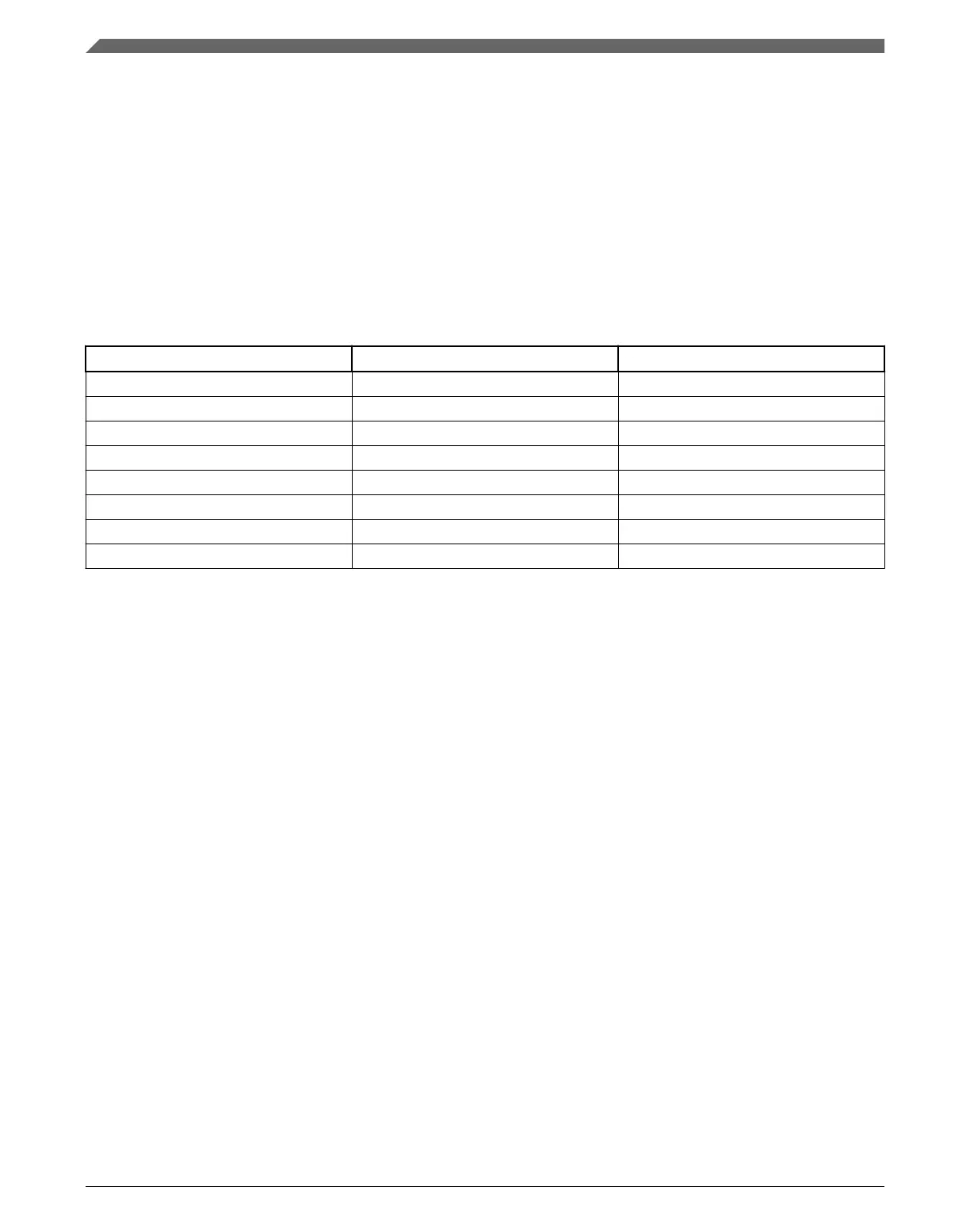

Table 3-62. Tx Buffer / FIFO / Queue Element Size

TXESC.TBDS[2:0] Data Field [bytes] Element Size [RAM words]

000 8 4

001 12 5

010 16 6

011 20 7

100 24 8

101 32 10

110 48 14

111 64 18

3.5.5.3 Tx FIFO

Tx FIFO operation is configured by programming TXBC[TFQM] to 0. Messages stored

in the Tx FIFO are transmitted starting with the message referenced by the Get Index

TXFQS[TFGI]. After each transmission the Get Index is incremented cyclically until the

Tx FIFO is empty. The Tx FIFO enables transmission of messages with the same

Message ID from different Tx Buffers in the order these messages have been written to

the Tx FIFO. The M_CAN calculates the Tx FIFO Free Level TXFQS[TFFL] as

difference between Get and Put Index. It indicates the number of available (free) Tx

FIFO elements.

New transmit messages have to be written to the Tx FIFO starting with the Tx Buffer

referenced by the Put Index TXFQS[TFQPI]. An Add Request increments the Put Index

to the next free Tx FIFO element. When the Put Index reaches the Get Index, Tx FIFO

Full (TXFQS[TFQF] = 1) is signalled. In this case no further messages should be written

to the Tx FIFO until the next message has been transmitted and the Get Index has been

incremented.

When a single message is added to the Tx FIFO, the transmission is requested by writing

a 1 to the TXBAR bit related to the Tx Buffer referenced by the Tx FIFO's Put Index.

Functional Description

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

110 Freescale Semiconductor, Inc.

Loading...

Loading...