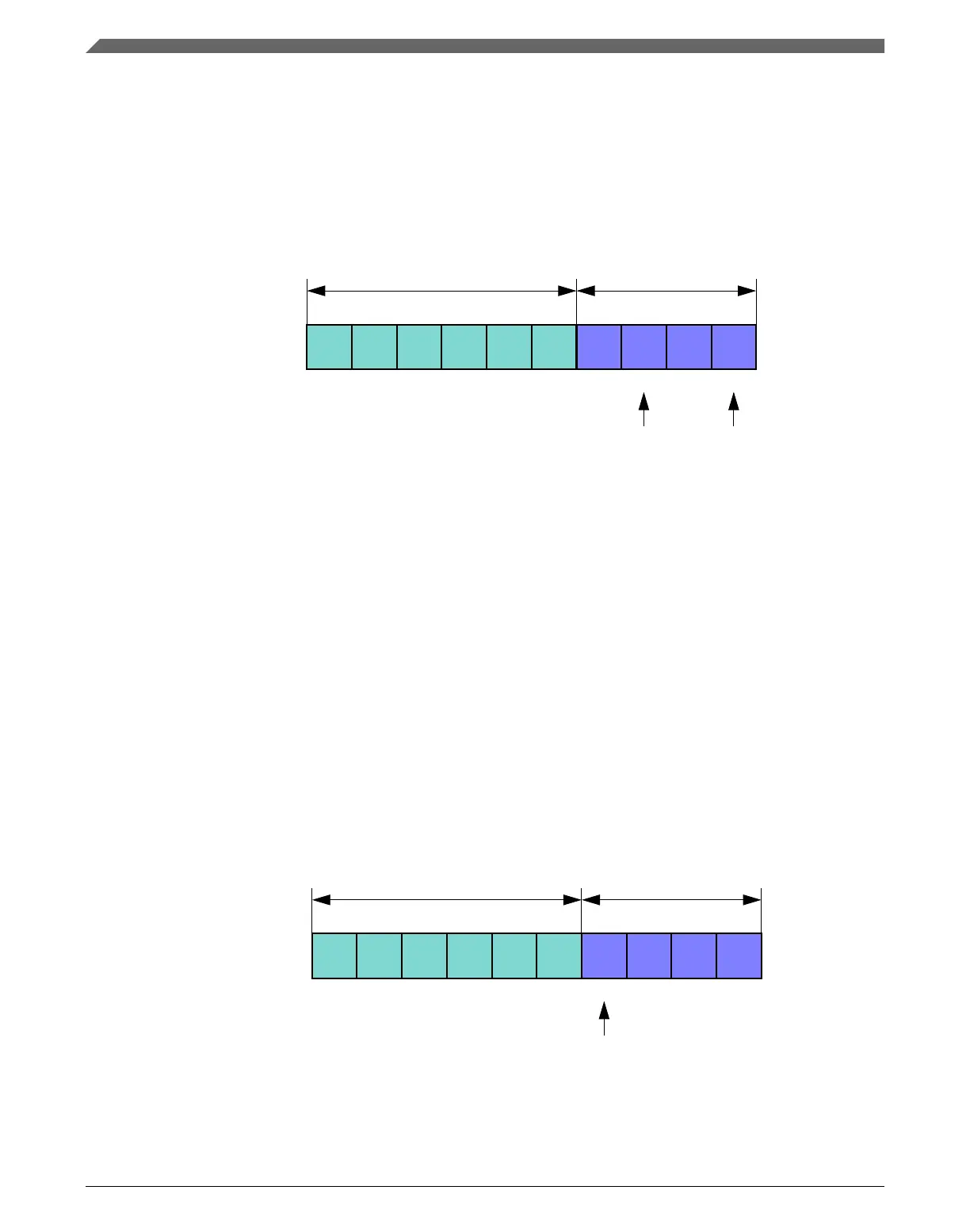

3.5.5.5 Mixed Dedicated Tx Buffers / Tx FIFO

In this case the Tx Buffers section in the Message RAM is subdivided into a set of

Dedicated Tx Buffers and a Tx FIFO. The number of Dedicated Tx Buffers is configured

by TXBC[NDTB]. The number of Tx Buffers assigned to the Tx FIFO is configured by

TXBC[TFQS]. In case TXBC[TFQS] is programmed to zero, only Dedicated Tx Buffers

are used.

Tx Sequence

Buffer Index

Put Index

Get Index

Tx FIFO

Dedicated Tx Buffers

1.

5.

4. 6.

2.

3.

0

1

2

3

4

5

6 7

8

9

ID3

ID15

ID8

ID24

ID4

ID2

Figure 3-58. Example of mixed Configuration Dedicated Tx Buffers / Tx FIFO

Tx prioritization:

• Scan Dedicated Tx Buffers and oldest pending Tx FIFO Buffer (referenced by

TXFS[TFGI])

• Buffer with lowest Message ID gets highest priority and is transmitted next

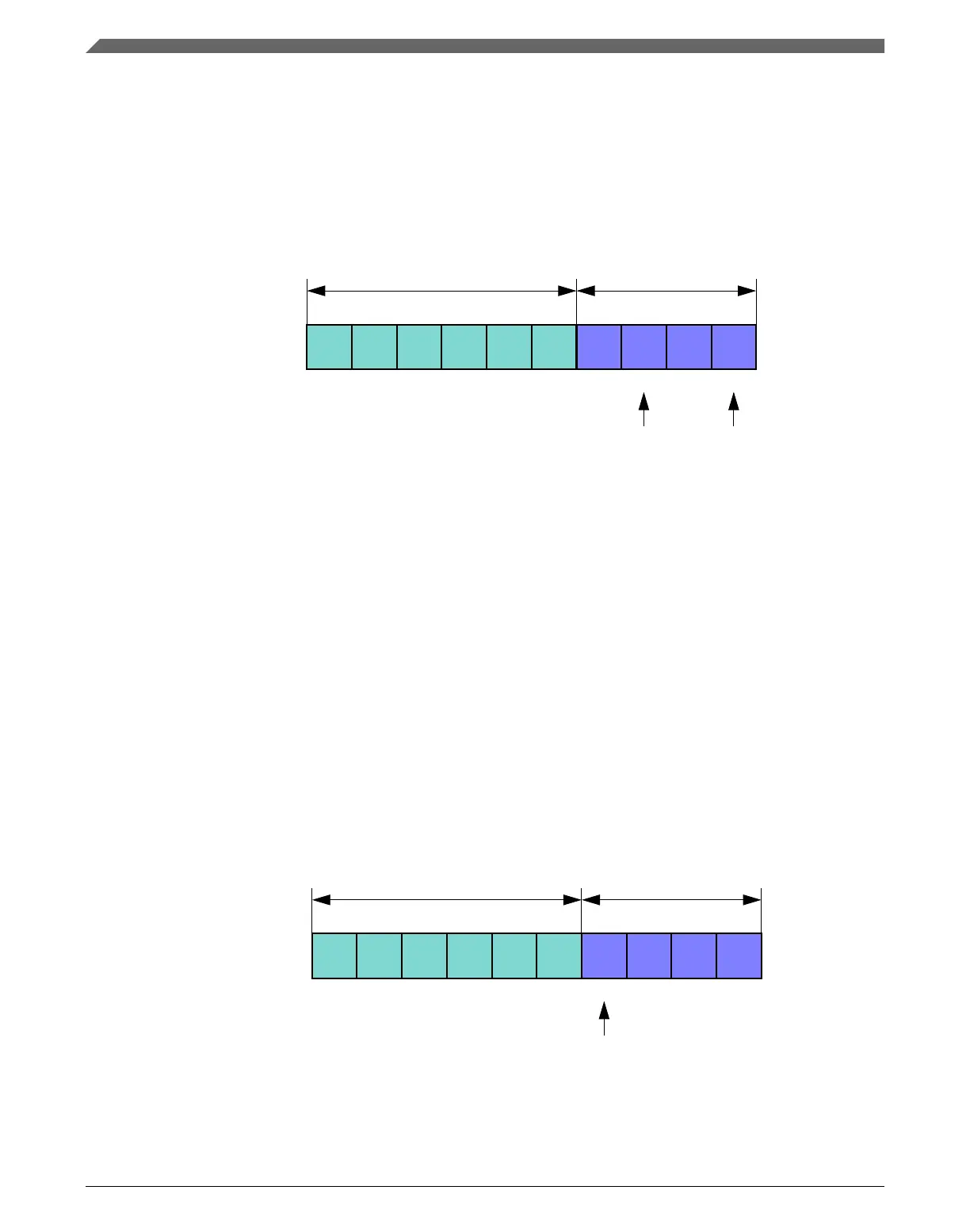

3.5.5.6 Mixed Dedicated Tx Buffers / Tx Queue

In this case the Tx Buffers section in the Message RAM is subdivided into a set of

Dedicated Tx Buffers and a Tx Queue. The number of Dedicated Tx Buffers is

configured by TXBC.NDTB. The number of Tx Queue Buffers is configured by

TXBC.TFQS. In case TXBC.TFQS is programmed to zero, only Dedicated Tx Buffers

are used.

Tx Sequence

Buffer Index

Put Index

Dedicated Tx Buffers

2.

5.

4. 6.

3.

1.

0

1

2

3

4

5

6

7

8

9

ID3

ID15

ID8

ID24

ID4

ID2

Tx Queue

Figure 3-59. Example of mixed Configuration Dedicated Tx Buffers / Tx Queue

Tx prioritization:

Functional Description

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

112 Freescale Semiconductor, Inc.

Loading...

Loading...