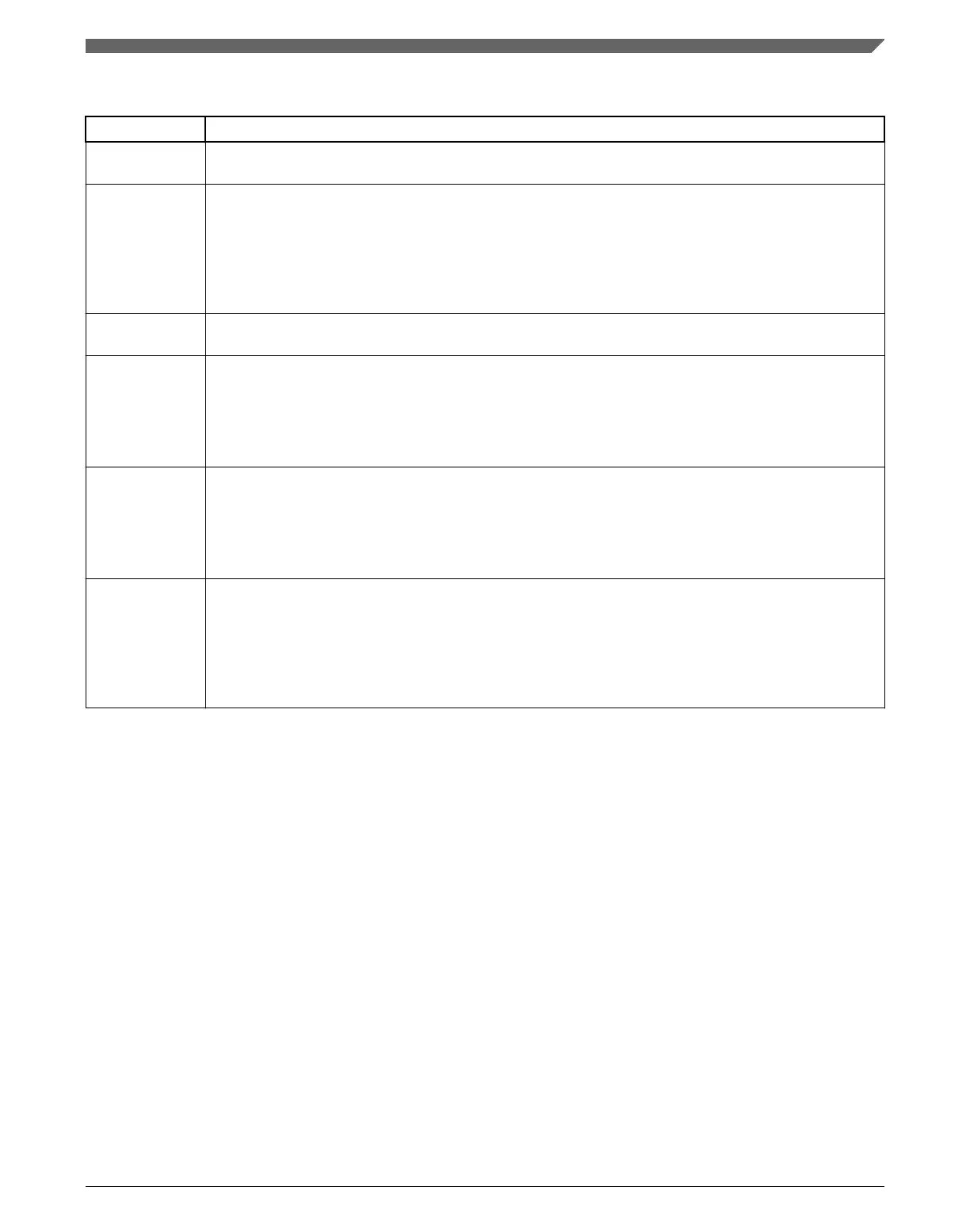

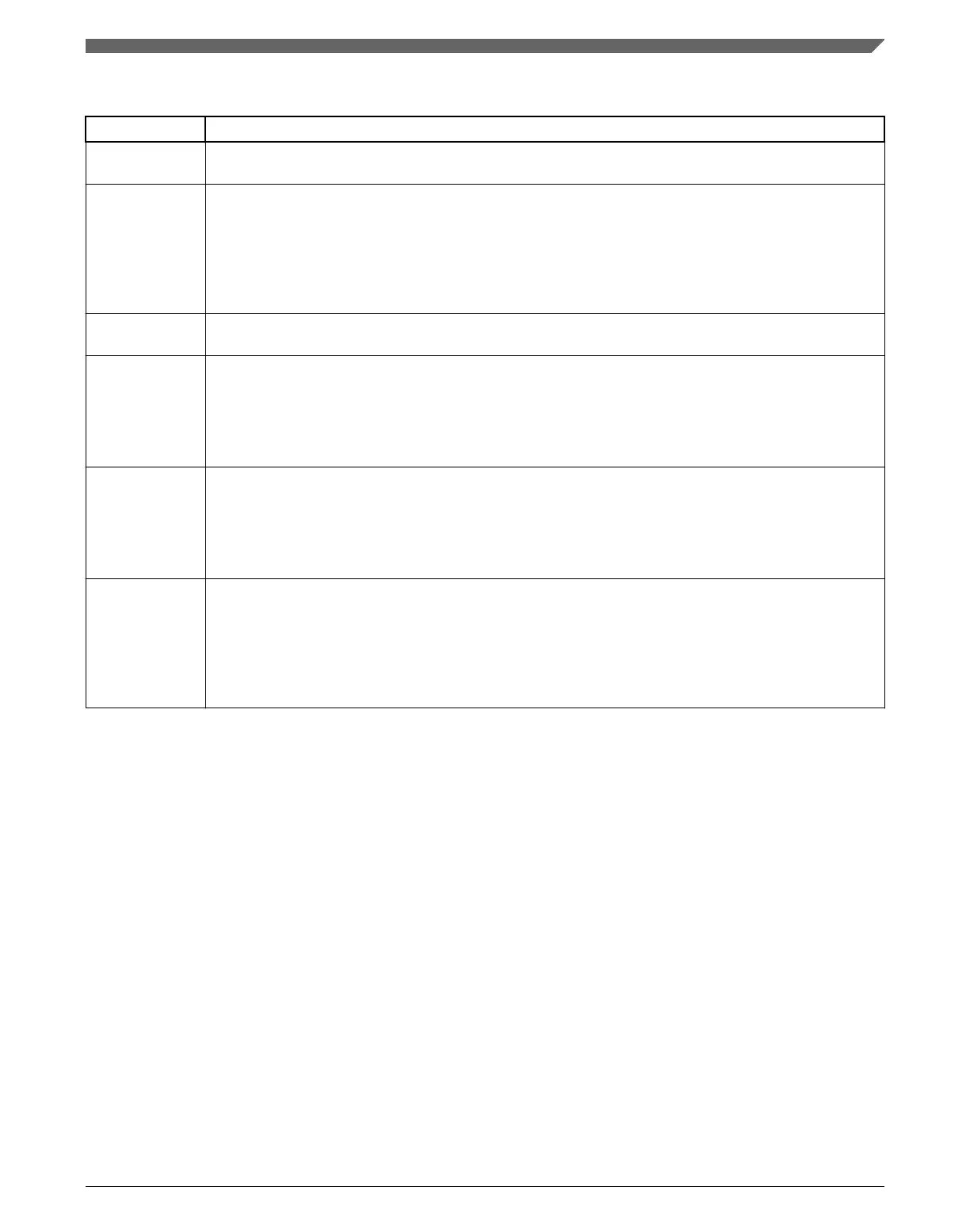

PCM_IAHB_BE1 field descriptions (continued)

Field Description

0 Burst reads are converted into a series of single transactions on the slave side of the gasket.

1 Burst reads are optimized for best system performance.

23

BWE_CORE0_D

Burst Write Enable Core0 Data

This bit controls the bus gasket’s handling of burst write transactions.

0 Burst writes are converted into a series of single transactions on the slave side of the gasket.

1 Burst writes are optimized for best system performance. Note this setting treats writes as “imprecise”

such that an error response on any beat of the burst is reported on the last beat.

24–28

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

29

PRE_CORE0_I

Pending Read Enable Core0 Instruction

This bit controls the bus gasket’s handling of pending read transactions.

0 Pending reads are disabled.

1 Pending reads are enabled.

30

BRE_CORE0_I

Burst Read Enable Core0 Instruction

This bit controls the bus gasket’s handling of burst read transactions.

0 Burst reads are converted into a series of single transactions on the slave side of the gasket.

1 Burst reads are optimized for best system performance.

31

BWE_CORE0_I

Burst Write Enable Core0 Instruction

This bit controls the bus gasket’s handling of burst write transactions.

0 Burst writes are converted into a series of single transactions on the slave side of the gasket.

1 Burst writes are optimized for best system performance. Note this setting treats writes as “imprecise”

such that an error response on any beat of the burst is reported on the last beat.

Chapter 2 Platform Configuration Module (PCM)

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 15

Loading...

Loading...