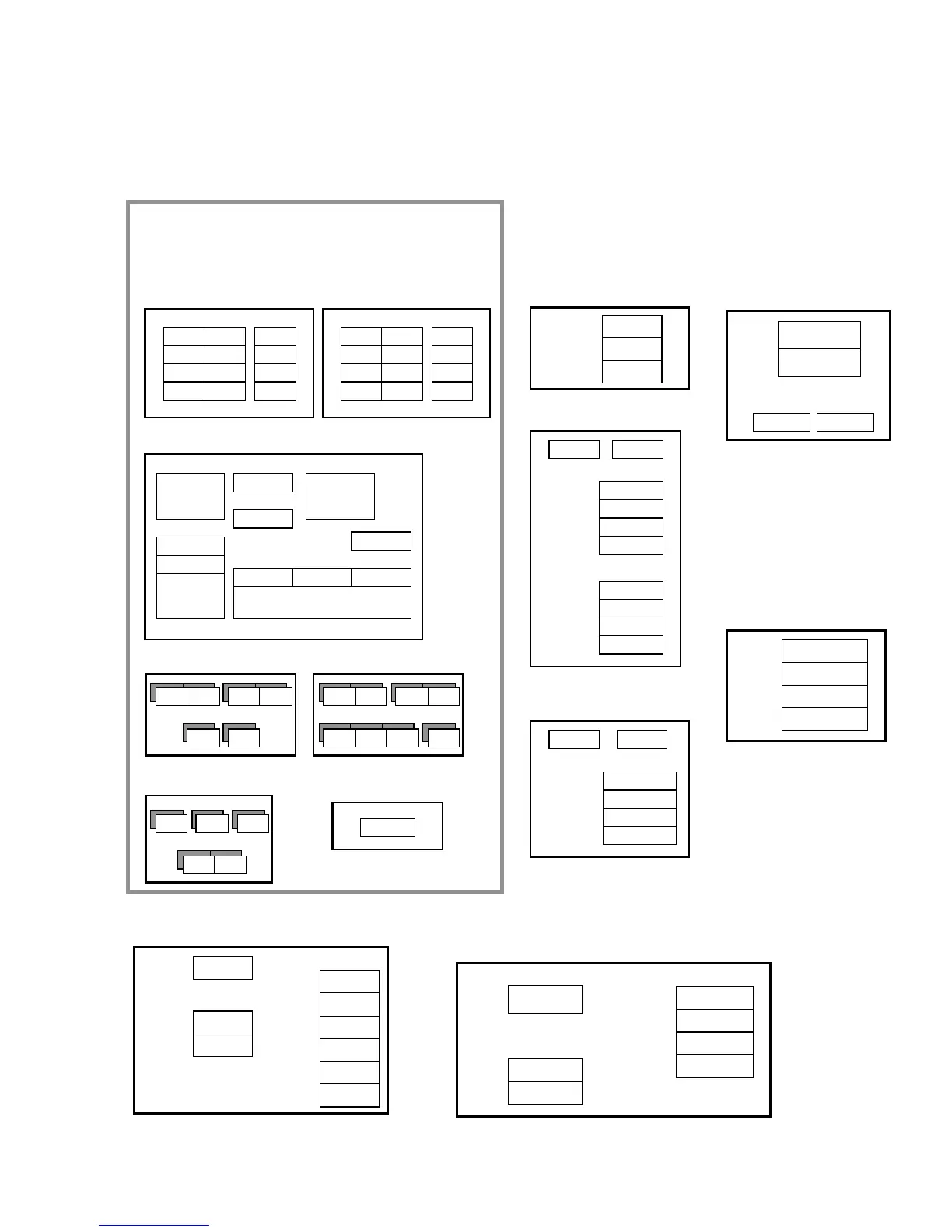

12Programming Model

12 – 3

ALU MAC

SHIFTER

PROGRAM SEQUENCER

I3

I0

I1

I2

L0

L1

L2

L3

CNTR

OWRCNTR

PX

COUNT

STACK

4 X 14

ASTAT

STATUS STACK*

MSTAT*IMASK*

PC

STACK

16 X 14

LOOP

STACK

4 X 18

IFC*

ICNTL

SSTAT

AX0 AX1 AY1AY0

AFAR

MX0 MX1 MY1MY0

MR0MR1MR2 MF

SR0SR1

SI SE SB

HOST INTERFACE PORT

(ADSP-2171, ADSP-2111, ADSP-21msp5x)

HMASK

HSR7

HSR6

0x3FE8

0x3FE7

0x3FE6

HDR5

HDR4

HDR3

0x3FE5

0x3FE4

0x3FE3

HDR2

HDR1

HDR0

0x3FE2

0x3FE1

0x3FE0

Status Registers

Data Registers

M0

M1

M2

14 1414

M3

14 1414

M5

M6

M7I7

I4

I5

I6

L5

L6

L7

M4L4

14

18 14

58

8

8

8

BUS EXCHANGE

5

81616

* Width and depth vary with processor

DATA ADDRESS GENERATORS

(DM addressing only) (DM and PM addressing)

Bit-reverse capability Indirect branch capability

DAG1 DAG2

SPORT 0

RX0 TX0

SPORT0 Control

0x3FFA

0x3FF9

0x3FF8

0x3FF7

Multichannel enables

RX 31-16

RX 15-0

TX 31-16

TX 15-0

0x3FF6

0x3FF5

0x3FF4

0x3FF3

Control

SCLKDIV

RFSDIV

Autobuffer

RX1 TX1

SPORT 1

SPORT1 Control

0x3FF2

0x3FF1

0x3FF0

0x3FEF

Control

SCLKDIV

RFSDIV

Autobuffer

TIMER

TPERIOD

TCOUNT

TSCALE

0x3FFD

0x3FFC

0x3FFB

IDMA PORT

BDMA PORT

PROGRAMMABLE FLAGS

(ADSP-2181)

0x3FE0

BWCOUNT

BDMA Control

BEAD

0x3FE4

0x3FE3

0x3FE2

BIAD

0x3FE1

IDMA Control

Register

BDMA Registers

0x3FE6

PFTYPE

0x3FE5 PFDATA

IDMA Registers

Programmable

Flag Registers

MEMORY INTERFACE

0x3FFF

System Control

Register

0x3FFE

Wait States

PMOVLAY

3

DMOVLAY

3

(ADSP-2181)

Autobuffer

Control

ADC Receive

0x3FEC

0x3FED

0x3FEE

0x3FEF

DAC Transmit

ANALOG INTERFACE

(ADSP-21msp5x)

Processor Core

Figure 12.1 ADSP-21xx Registers

Shading denotes secondary (alternate) registers.

Registers are 16 bits wide (unless otherwise marked).

Loading...

Loading...