iSeries architecture: Fundamental strength of the IBM ^ i5 and iSeries 17

Draft Document for Review October 18, 2004 5486AdvTech.fm

processors is 4.4 times as powerful as its predecesor POWER4 generation of

microprocessors.

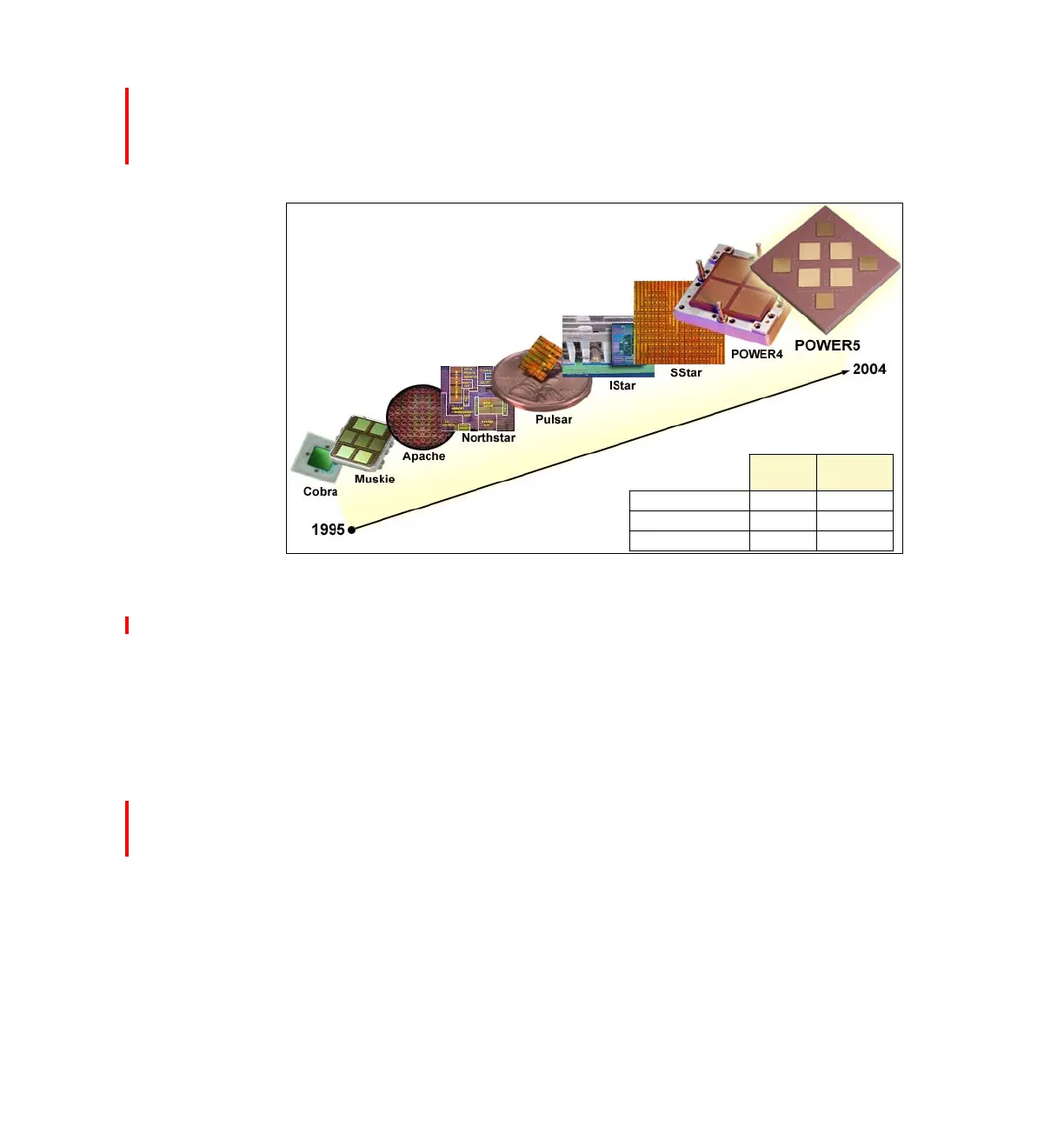

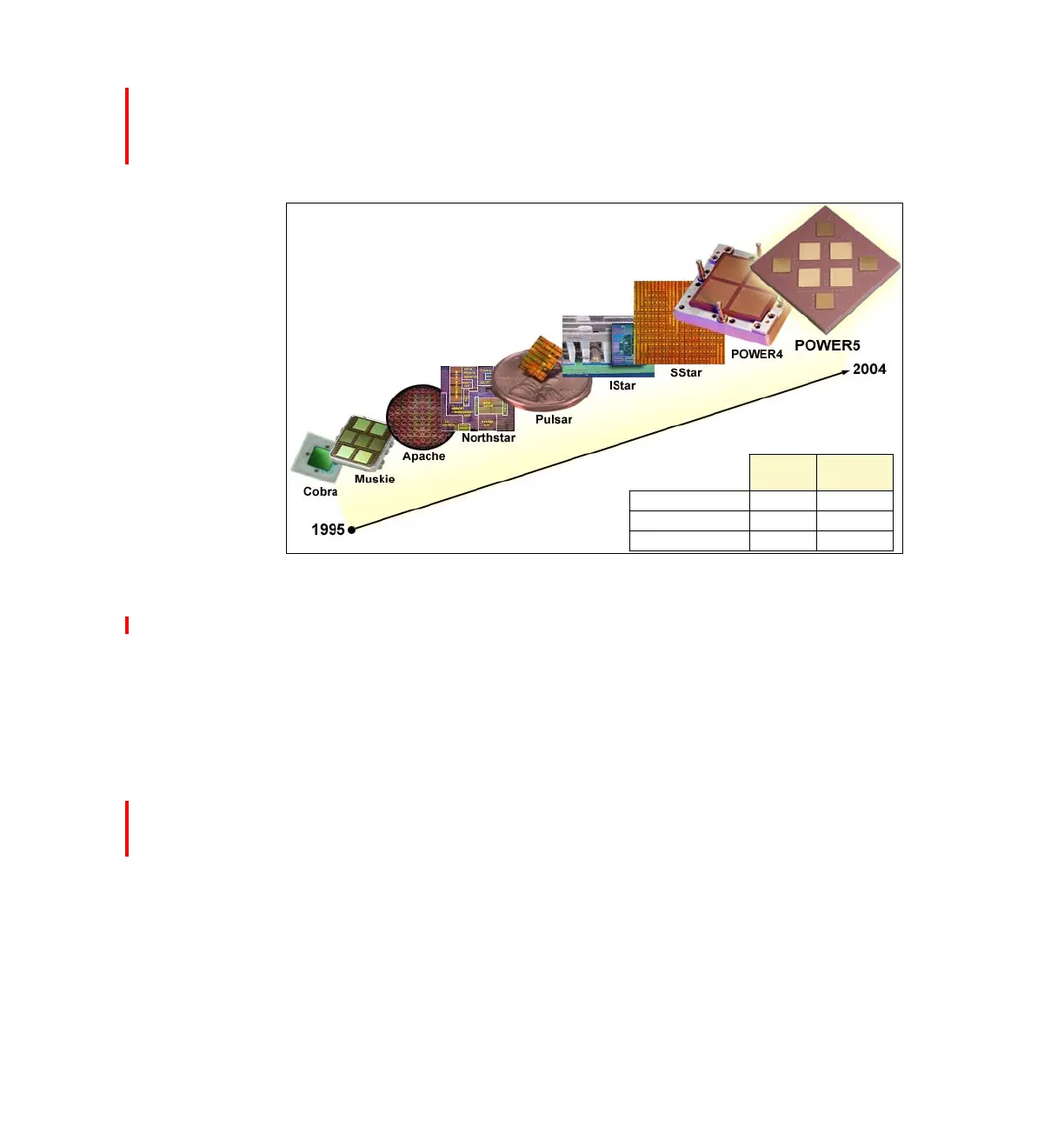

The advance in processor technology is shown in the following figure.

Pulsar, ISTAR, and SSTAR processors use on-chip copper-wiring technology.

The Pulsar processors integrate IBM CMOS7S technology. ISTAR and SSTAR

processors integrate CMOS8S technology. Previously, Northstar technology

used aluminum for on-chip wiring. Copper's better conductivity permits thinner

wires to be used, which enables the transistors to be packed closer together. The

denser new technology permits additional micro-architecture methods to improve

performance.

Delivered in 2002, the next evolution of IBM Eserver microprocessors was

POWER4 fabricated in CMOS8S technology. Keeping multiple levels of high

speed cache is still necessary to keep the processors busy. Denser processor

technology permits more on-chip cache.

Continuing this industry-leading technology, POWER5 in CMOS9S today. The

improved density with CMOS9S technology allows for larger caches, and for

cache-controllers and memory controllers to be on-chip, resulting in higher

processor performance.

This growth and implementation of new technology is possible because of the

iSeries TIMI layer. TIMI allows the system to incorporate significant new

hardware technology quickly and transparently. The ease with which customers

>= 1.5 GHz50 MHz Frequency

Up to 254*NoneLogical Partitions

276M4.7MTransistor count

2004

POWER5

1995

Cobra

>= 1.5 GHz50 MHz Frequency

Up to 254*NoneLogical Partitions

276M4.7MTransistor count

2004

POWER5

1995

Cobra

1999

2000

2001

2002

Loading...

Loading...