Timer Interface Module B (TIMB)

Functional Description

MC68HC908AB32 — Rev. 1.0 Technical Data

MOTOROLA Timer Interface Module B (TIMB) 199

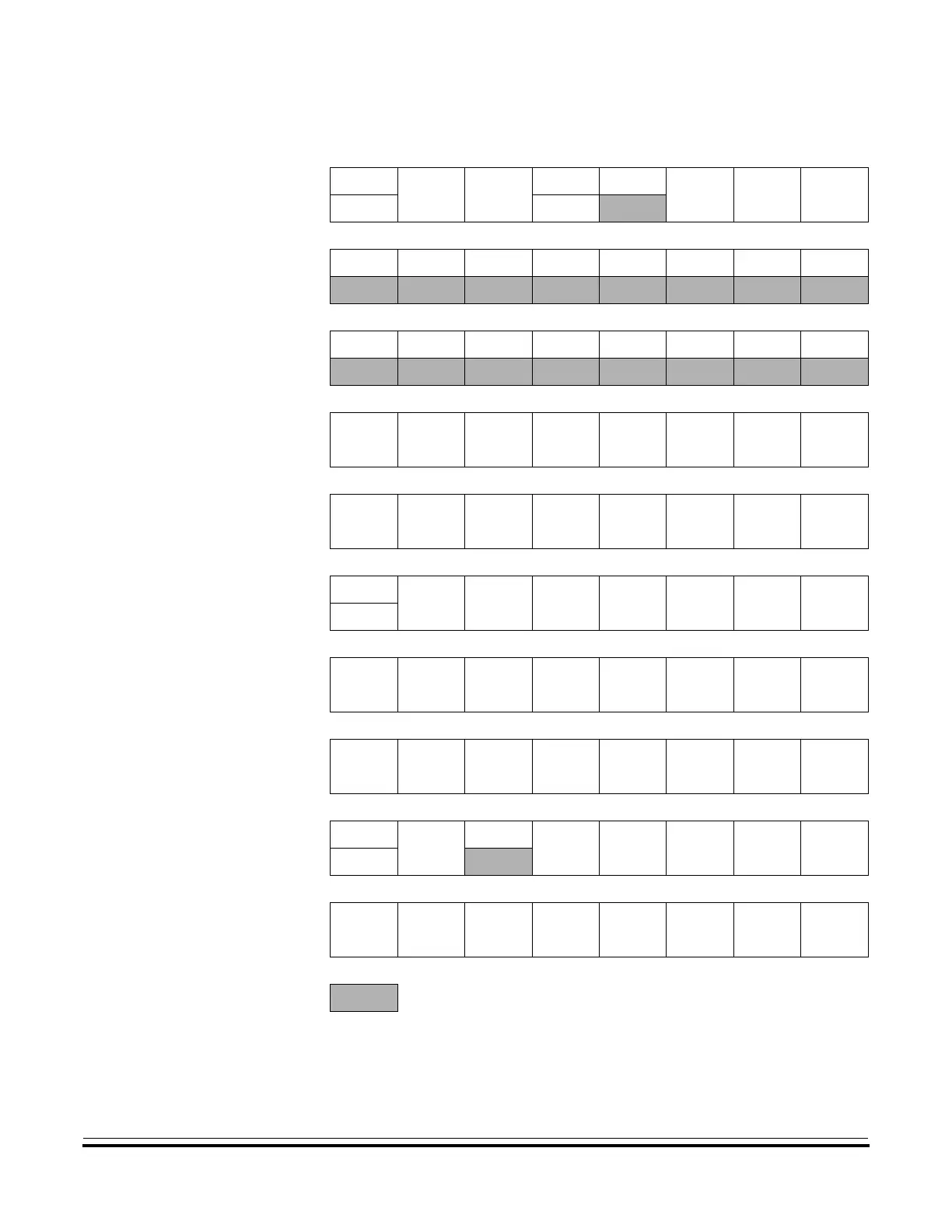

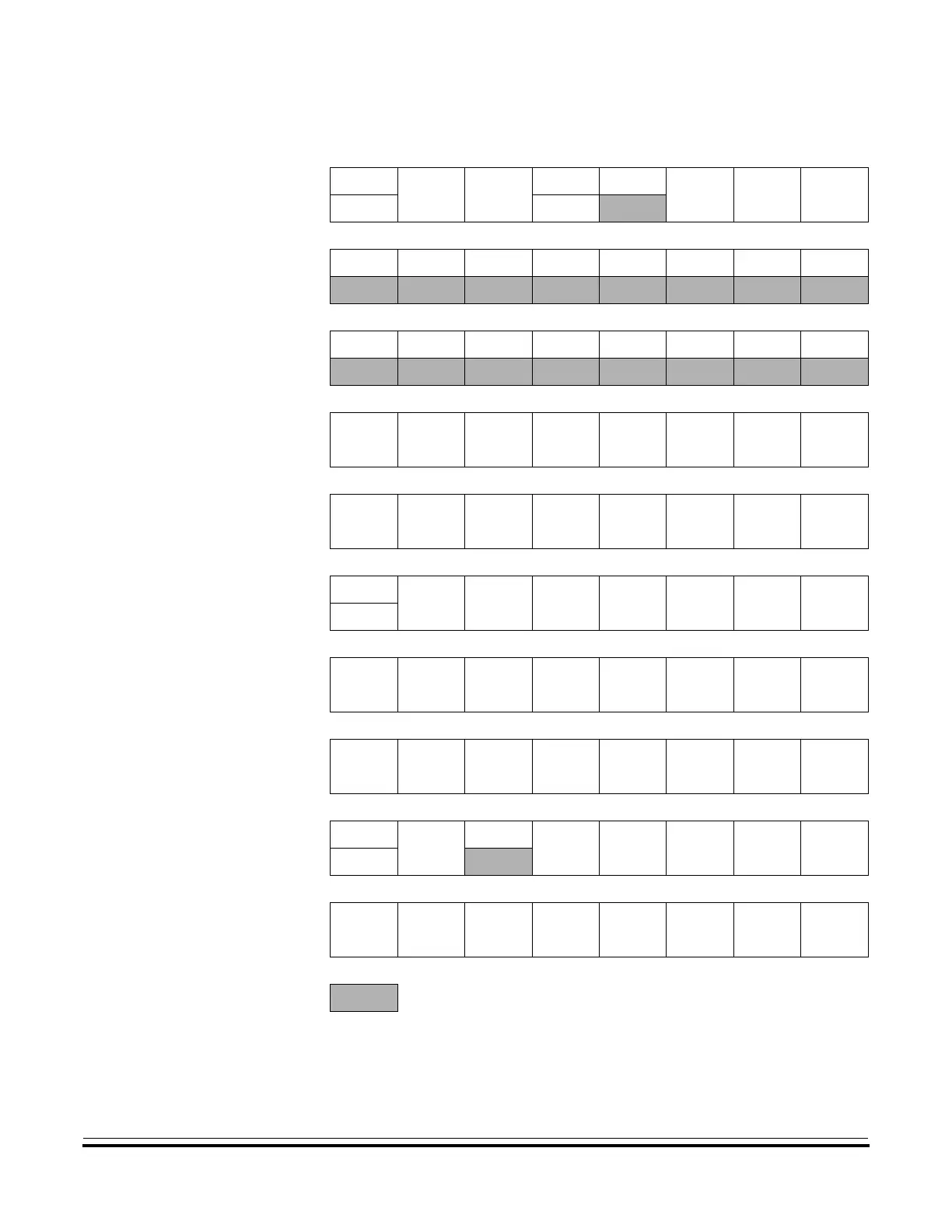

Addr. Register Name Bit 7 654321Bit 0

$0040

Timer B Status and

Control Register

(TBSC)

Read: TOF

TOIE TSTOP

00

PS2 PS1 PS0

Write: 0 TRST

Reset: 00100000

$0041

Timer B Counter

Register High

(TBCNTH)

Read: Bit 15 14 13 12 11 10 9 Bit 8

Write:

Reset: 00000000

$0042

Timer B Counter

Register Low

(TBCNTL)

Read: Bit 7 654321Bit 0

Write:

Reset: 00000000

$0043

Timer B Counter Modulo

Register High

(TBMODH)

Read:

Bit 15 14 13 12 11 10 9 Bit 8

Write:

Reset: 11111111

$0044

Timer B Counter Modulo

Register Low

(TBMODL)

Read:

Bit 7 654321Bit 0

Write:

Reset: 11111111

$0045

Timer B Channel 0 Status

and Control Register

(TBSC0)

Read: CH0F

CH0IE MS0B MS0A ELS0B ELS0A TOV0 CH0MAX

Write: 0

Reset: 00000000

$0046

Timer B Channel 0

Register High

(TBCH0H)

Read:

Bit 15 14 13 12 11 10 9 Bit 8

Write:

Reset: Indeterminate after reset

$0047

Timer B Channel 0

Register Low

(TBCH0L)

Read:

Bit 7 654321Bit 0

Write:

Reset: Indeterminate after reset

$0048

Timer B Channel 1 Status

and Control Register

(TBSC1)

Read: CH1F

CH1IE

0

MS1A ELS1B ELS1A TOV1 CH1MAX

Write: 0

Reset: 00000000

$0049

Timer B Channel 1

Register High

(TBCH1H)

Read:

Bit 15 14 13 12 11 10 9 Bit 8

Write:

Reset: Indeterminate after reset

= Unimplemented

Figure 12-2. TIMB I/O Register Summary (Sheet 1 of 2)

Loading...

Loading...