General Description

Technical Data MC68HC908AB32 — Rev. 1.0

32 General Description MOTOROLA

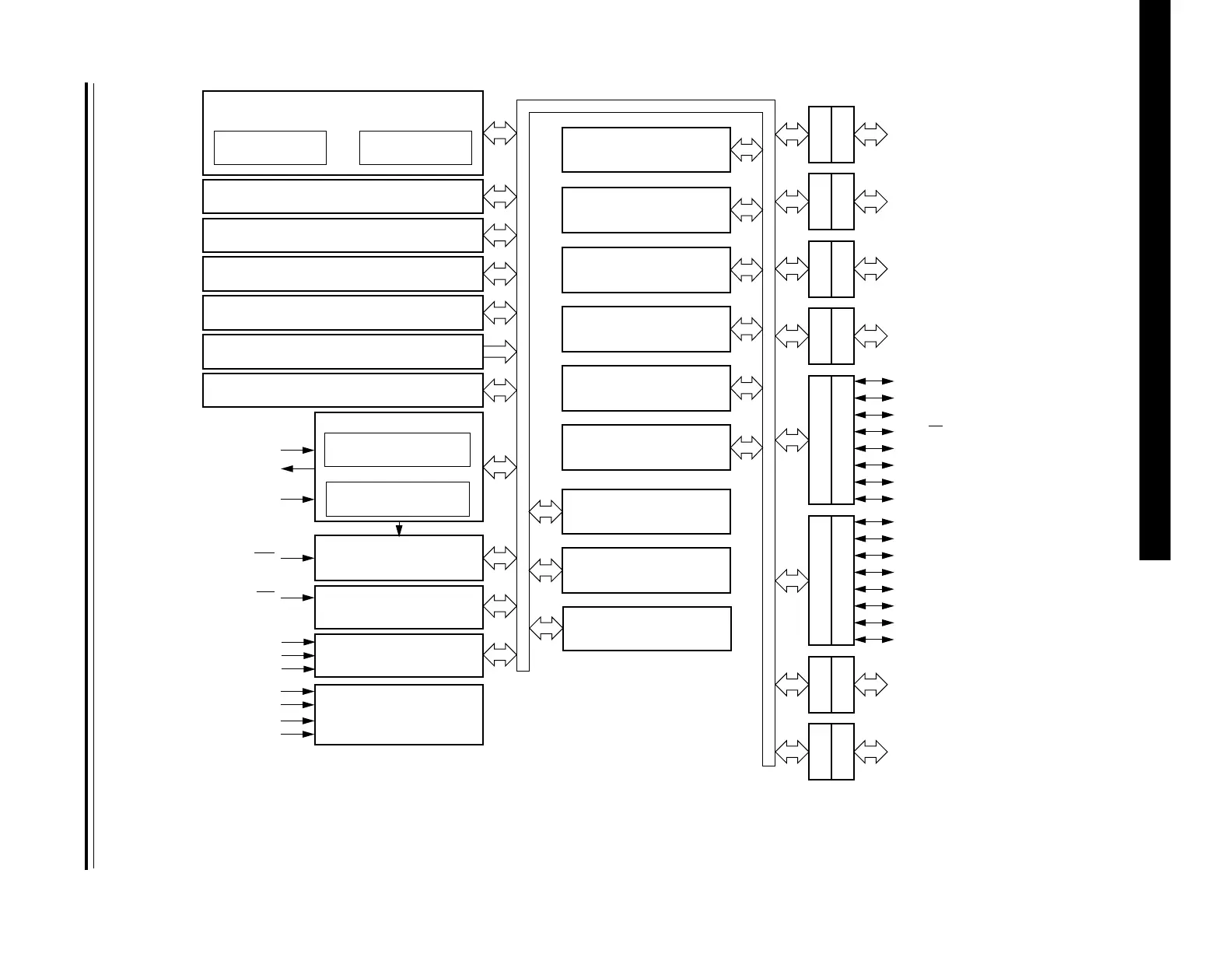

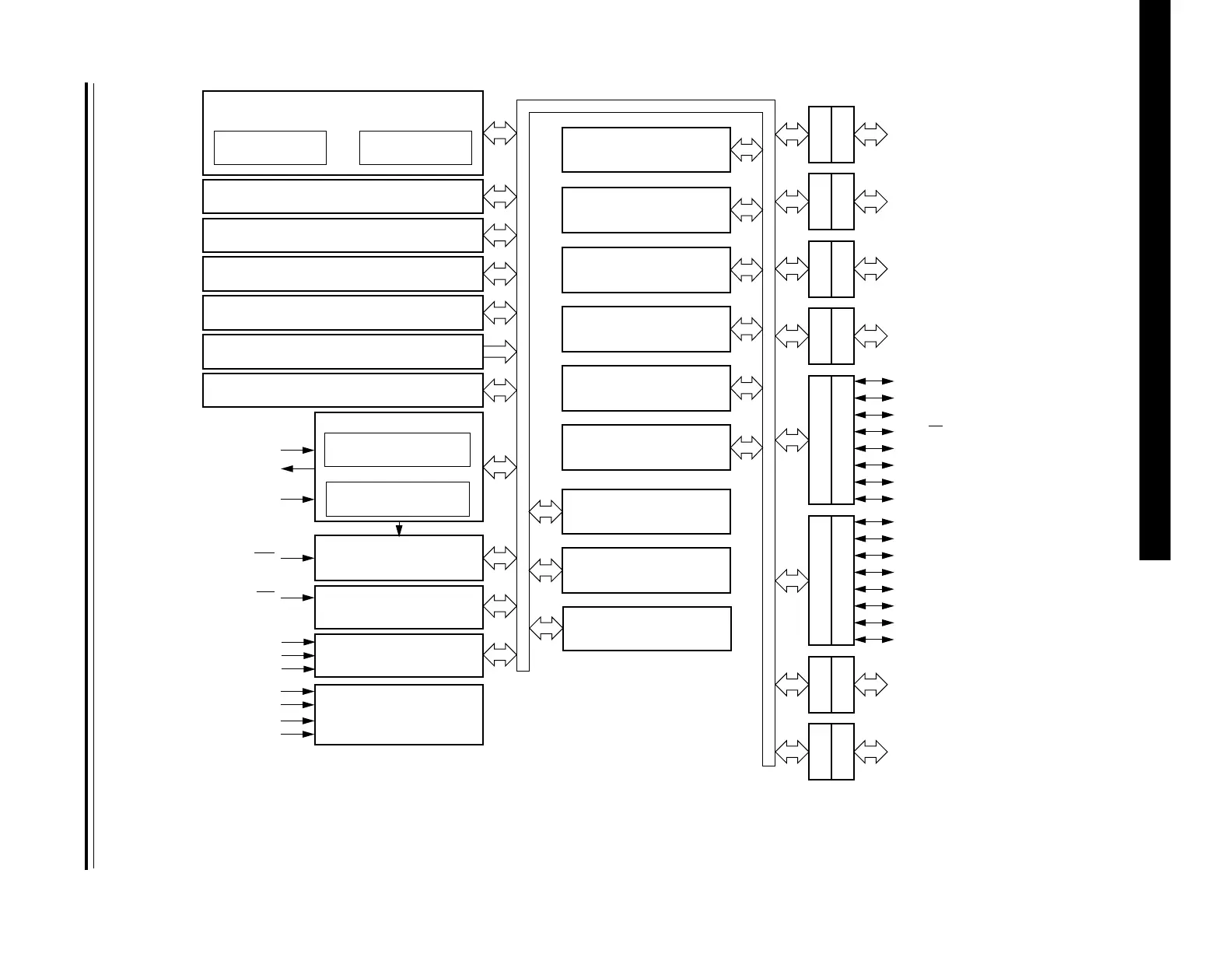

Figure 1-1. MC68HC908AB32 Block Diagram

CLOCK GENERATOR MODULE

SYSTEM INTEGRATION

MODULE

SERIAL PERIPHERAL

4-CHANNEL TIMER INTERFACE

MODULE B

LOW-VOLTAGE

INHIBIT MODULE

KEYBOARD

ARITHMETIC/LOGIC

UNIT (ALU)

CPU

REGISTERS

M68HC08 CPU

CONTROL AND STATUS REGISTERS — 80 BYTES

USER FLASH — 32,256 BYTES

USER RAM — 1024 BYTES

MONITOR ROM — 307 BYTES

USER FLASH VECTORS — 48 BYTES

SINGLE EXTERNAL IRQ

MODULE

PORTA

DDRA

DDRE

PORTE

INTERNAL BUS

OSC1

OSC2

CGMXFC

* RST

* IRQ

INTERFACE MODULE

INTERRUPT MODULE

COMPUTER OPERATING

PROPERLY MODULE

PTA7 – PTA0

V

REFH

PTE7/SPSCK

PTE6/MOSI

PTE5/MISO

PTE4/SS

PTE3/TACH1

PTE2/TACH0

PTE1/RxD

PTE0/TxD

A

VSS

/V

REFL

4-CHANNEL TIMER INTERFACE

MODULE A

4.9125-MHz OSCILLATOR

PHASE-LOCKED LOOP

SERIAL COMMUNICATIONS

INTERFACE MODULE

POWER-ON RESET

MODULE

POWER

V

SS

V

DD

V

SSA

V

DDA

† Ports are software configurable with pullup device if input port.

‡ Higher current drive port pins

* Pin contains integrated pullup device

** Pullup enabled when configured as keyboard interrupt pin

V

DDAREF

8-BIT ANALOG-TO-DIGITAL

CONVERTER MODULE

USER EEPROM — 512 BYTES

PROGRAMMABLE INTERRUPT

TIMER MODULE

PORTB

DDRB

PTB7/ATD7 – PTB0/ATD0

PORTC

DDRC

PTC5 – PTC0

PORTD

DDRD

PTD7 – PTD0

†‡

DDRF

PORTF

PTF7

†

PTF6

†

PTF5/TBCH1

†

PTF4/TBCH0

†

PTF3/TBCH3

†

PTF2/TBCH2

†

PTF1/TACH3

†

PTF0/TACH2

†

PORTG

DDRG

PTG2/KBD2 – PTG0/KBD0 **

PORTH

DDRH

PTH1/KBD4 – PTH0/KBD3 **

(PTC2/MCLK)

(PTD6/TACLK)

(PTD4/TBCLK)

Loading...

Loading...