Serial Communications Interface

Technical Data MC68HC908AB32 — Rev. 1.0

264 Serial Communications Interface Module (SCI) MOTOROLA

PTY — Parity Bit

This read/write bit determines whether the SCI generates and checks

for odd parity or even parity. (See Table 15-5.) Reset clears the PTY

bit.

1 = Odd parity

0 = Even parity

NOTE:

Changing the PTY bit in the middle of a transmission or reception can

generate a parity error.

15.9.2 SCI Control Register 2

SCI control register 2:

• Enables the following CPU interrupt requests:

– Enables the SCTE bit to generate transmitter CPU interrupt

requests

– Enables the TC bit to generate transmitter CPU interrupt

requests

– Enables the SCRF bit to generate receiver CPU interrupt

requests

– Enables the IDLE bit to generate receiver CPU interrupt

requests

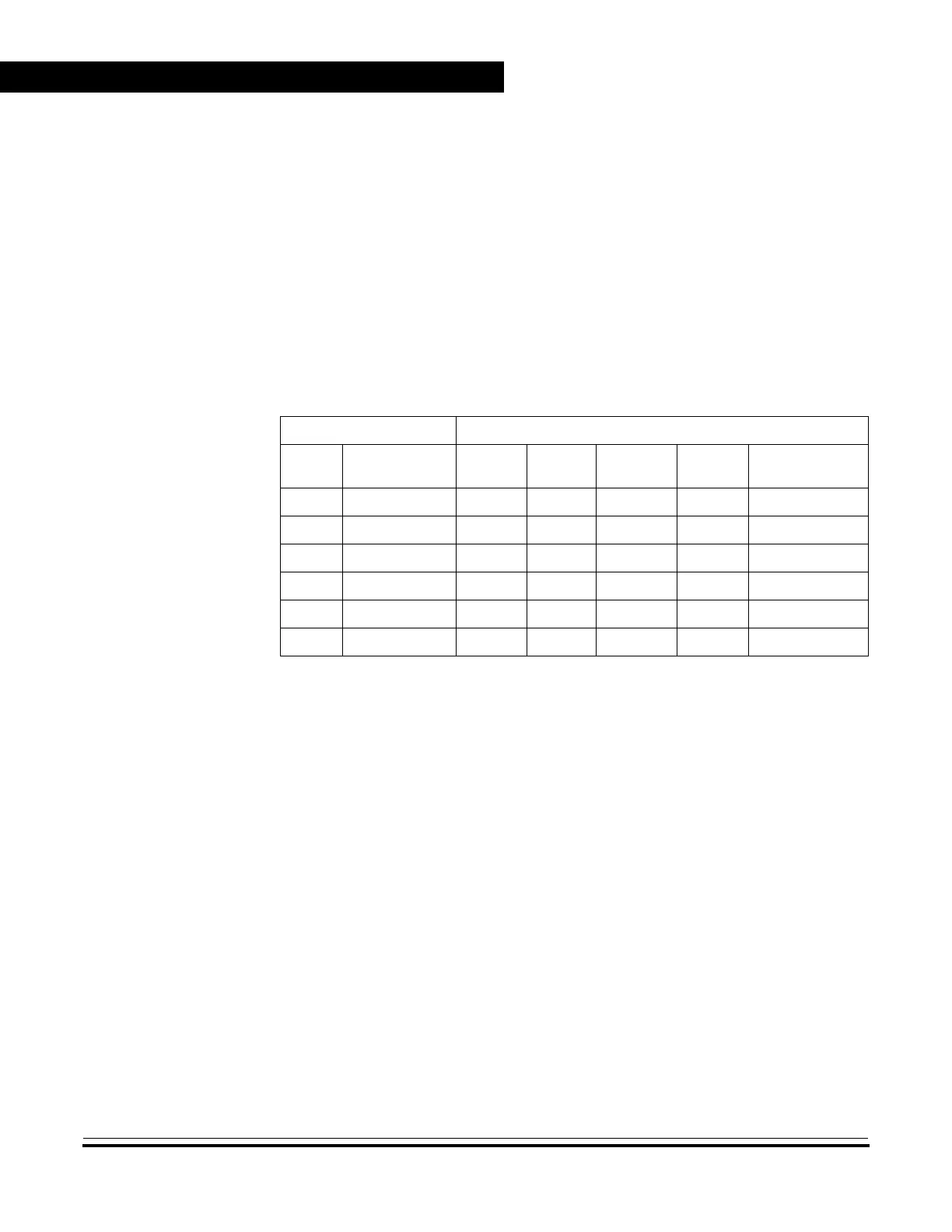

Table 15-5. Character Format Selection

Control Bits Character Format

M

PEN and

PTY

Start

Bits

Data

Bits

Parity

Stop

Bits

Character

Length

0 0X 1 8 None 1 10 bits

1 0X 1 9 None 1 11 bits

0 10 1 7 Even 1 10 bits

0 11 1 7 Odd 1 10 bits

1 10 1 8 Even 1 11 bits

1 11 1 8 Odd 1 11 bits

Loading...

Loading...