Serial Peripheral Interface Module (SPI)

Technical Data MC68HC908AB32 — Rev. 1.0

306 Serial Peripheral Interface Module (SPI) MOTOROLA

16.14.2 SPI Status and Control Register

The SPI status and control register contains flags to signal these

conditions:

• Receive data register full

• Failure to clear SPRF bit before next byte is received (overflow

error)

• Inconsistent logic level on SS

pin (mode fault error)

• Transmit data register empty

The SPI status and control register also contains bits that perform these

functions:

• Enable error interrupts

• Enable mode fault error detection

• Select master SPI baud rate

SPRF — SPI Receiver Full Bit

This clearable, read-only flag is set each time a byte transfers from

the shift register to the receive data register. SPRF generates a CPU

interrupt request if the SPRIE bit in the SPI control register is set also.

During an SPRF CPU interrupt, the CPU clears SPRF by reading the

SPI status and control register with SPRF set and then reading the

SPI data register. Reset clears the SPRF bit.

1 = Receive data register full

0 = Receive data register not full

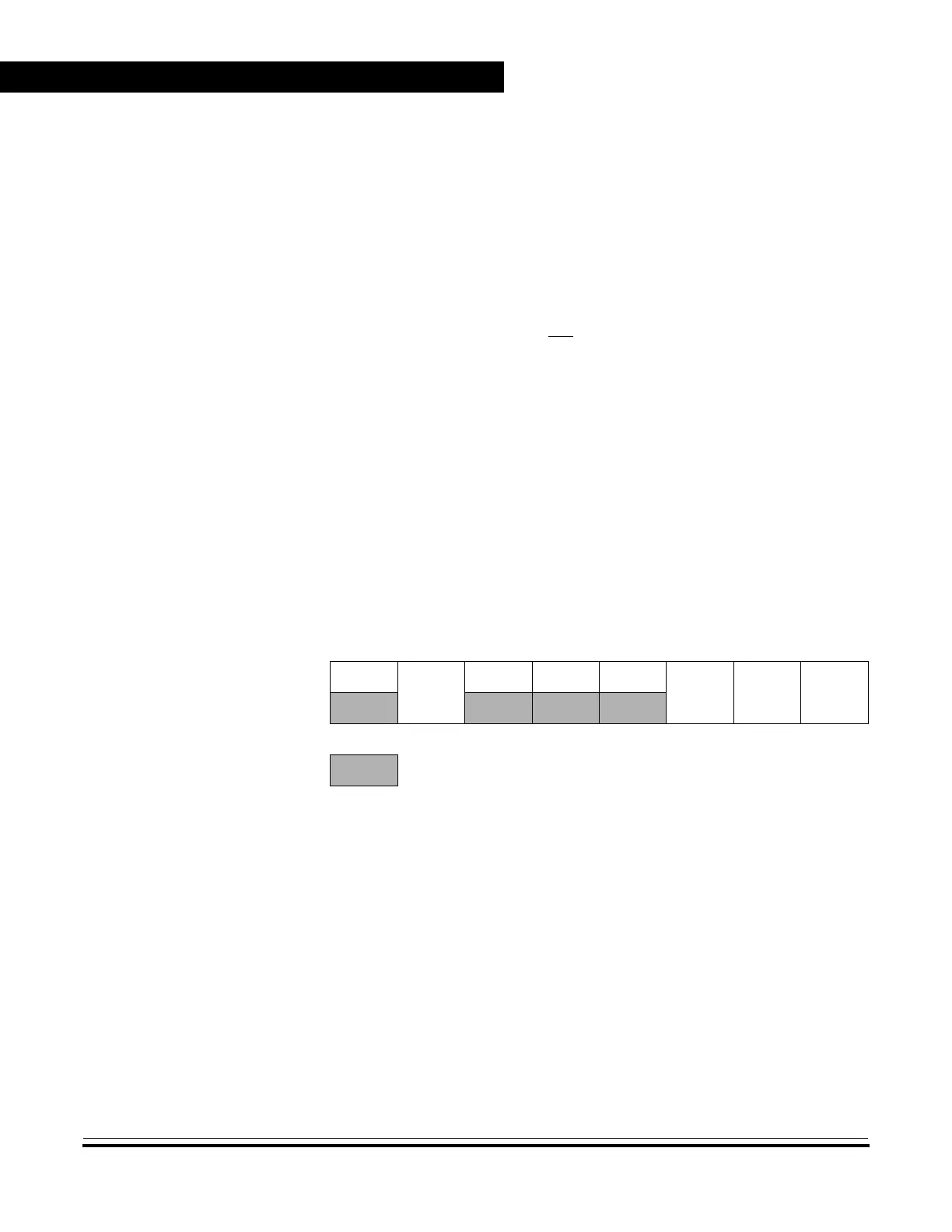

Address: $0011

Bit 7 654321Bit 0

Read: SPRF

ERRIE

OVRF MODF SPTE

MODFEN SPR1 SPR0

Write:

Reset: 00001000

= Unimplemented

Figure 16-14. SPI Status and Control Register (SPSCR)

Loading...

Loading...