FLASH Memory

Technical Data MC68HC908AB32 — Rev. 1.0

66 FLASH Memory MOTOROLA

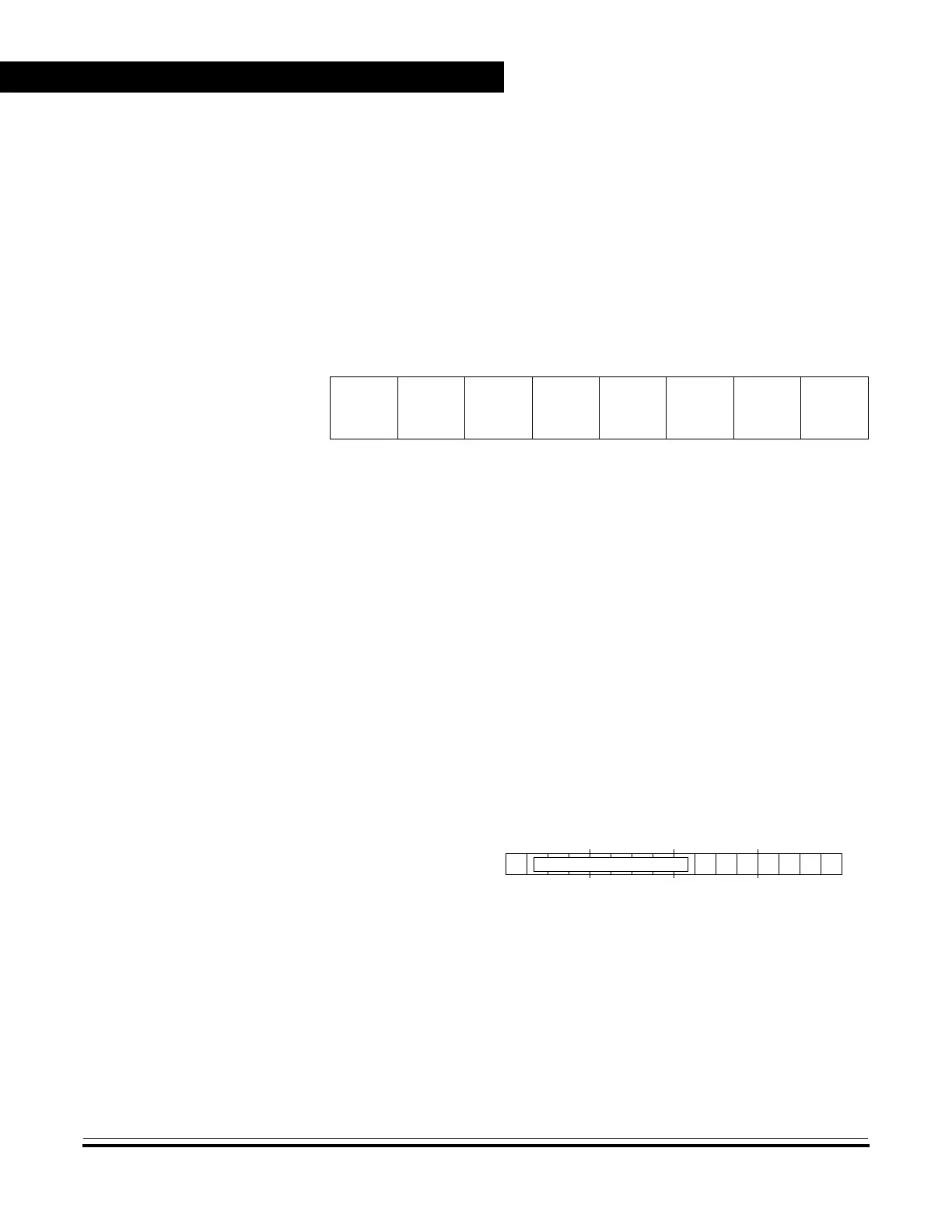

4.8.1 FLASH Block Protect Register

The FLASH block protect register (FLBPR) is implemented as a byte

within the FLASH memory, and therefore can only be written during a

programming sequence of the FLASH memory. The value in this register

determines the starting location of the protected range within the FLASH

memory.

BPR[7:0] — FLASH Block Protect Bits

These eight bits represent bits [14:7] of a 16-bit memory address.

Bit-15 is logic 1 and bits [6:0] are logic 0s.

The resultant 16-bit address is used for specifying the start address

of the FLASH memory for block protection. The FLASH is protected

from this start address to the end of FLASH memory, at $FFFF. With

this mechanism, the protect start address can be XX00 and XX80

(128 bytes page boundaries) within the FLASH memory.

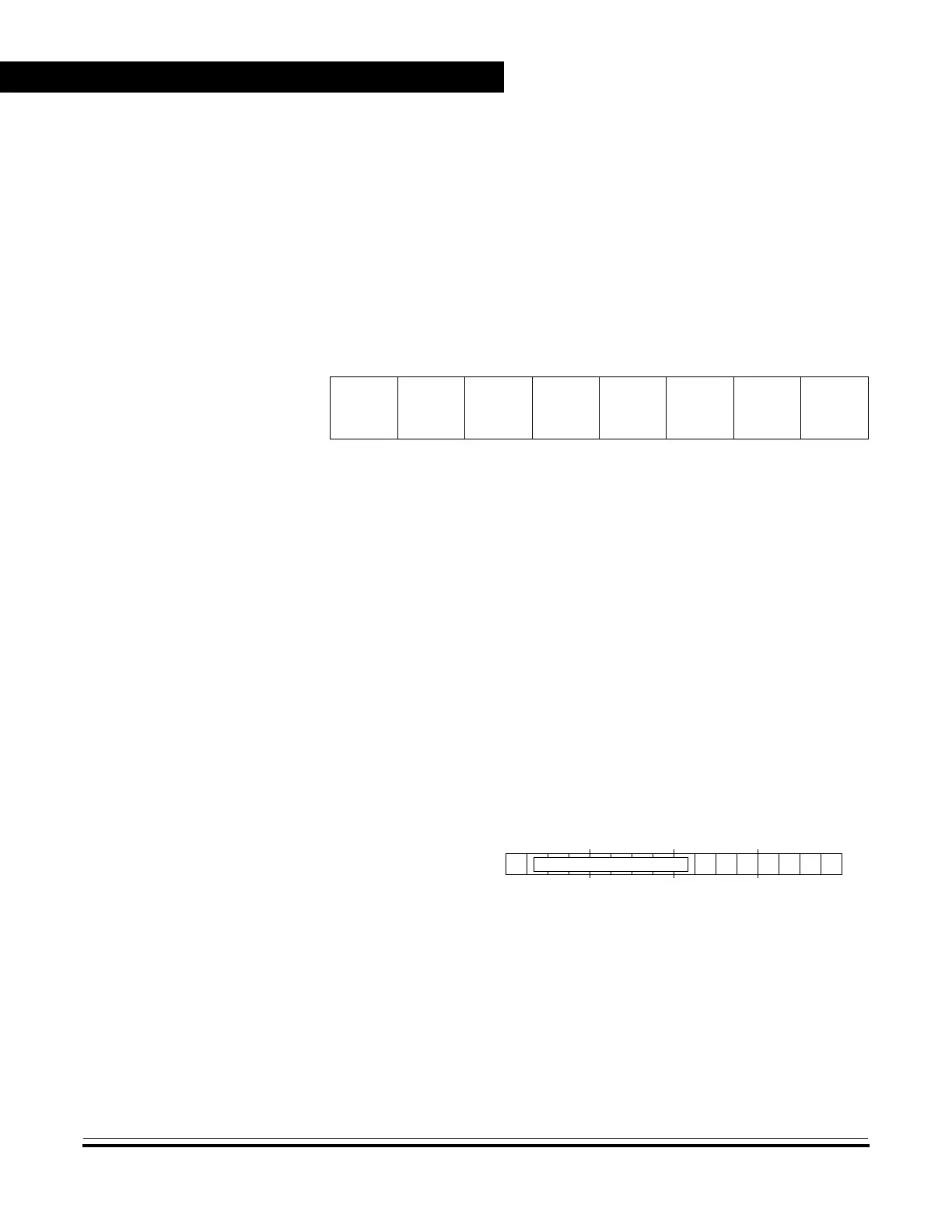

Figure 4-4. FLASH Block Protect Start Address

Address: $FF7E

Bit 7 654321Bit 0

Read:

BPR7 BPR6 BPR5 BPR4 BPR3 BPR2 BPR1 BPR0

Write:

Reset: UUUUUUUU

U = Unaffected by reset. Initial value from factory is 1.

Write to this register is by a programming sequence to the FLASH memory.

Figure 4-3. FLASH Block Protect Register (FLBPR)

1

FLBPR value

16-bit memory address

0000000

Start address of FLASH block protect

Loading...

Loading...