Programmable Interrupt Timer (PIT)

I/O Registers

MC68HC908AB32 — Rev. 1.0 Technical Data

MOTOROLA Programmable Interrupt Timer (PIT) 225

bits. Some status bits have a two-step read/write clearing procedure. If

software does the first step on such a bit before the break, the bit cannot

change during the break state as long as BCFE is at logic zero. After the

break, doing the second step clears the status bit.

13.7 I/O Registers

The following I/O registers control and monitor operation of the PIT:

• PIT status and control register (PSC)

• PIT counter registers (PCNTH:PCNTL)

• PIT counter modulo registers (PMODH:PMODL)

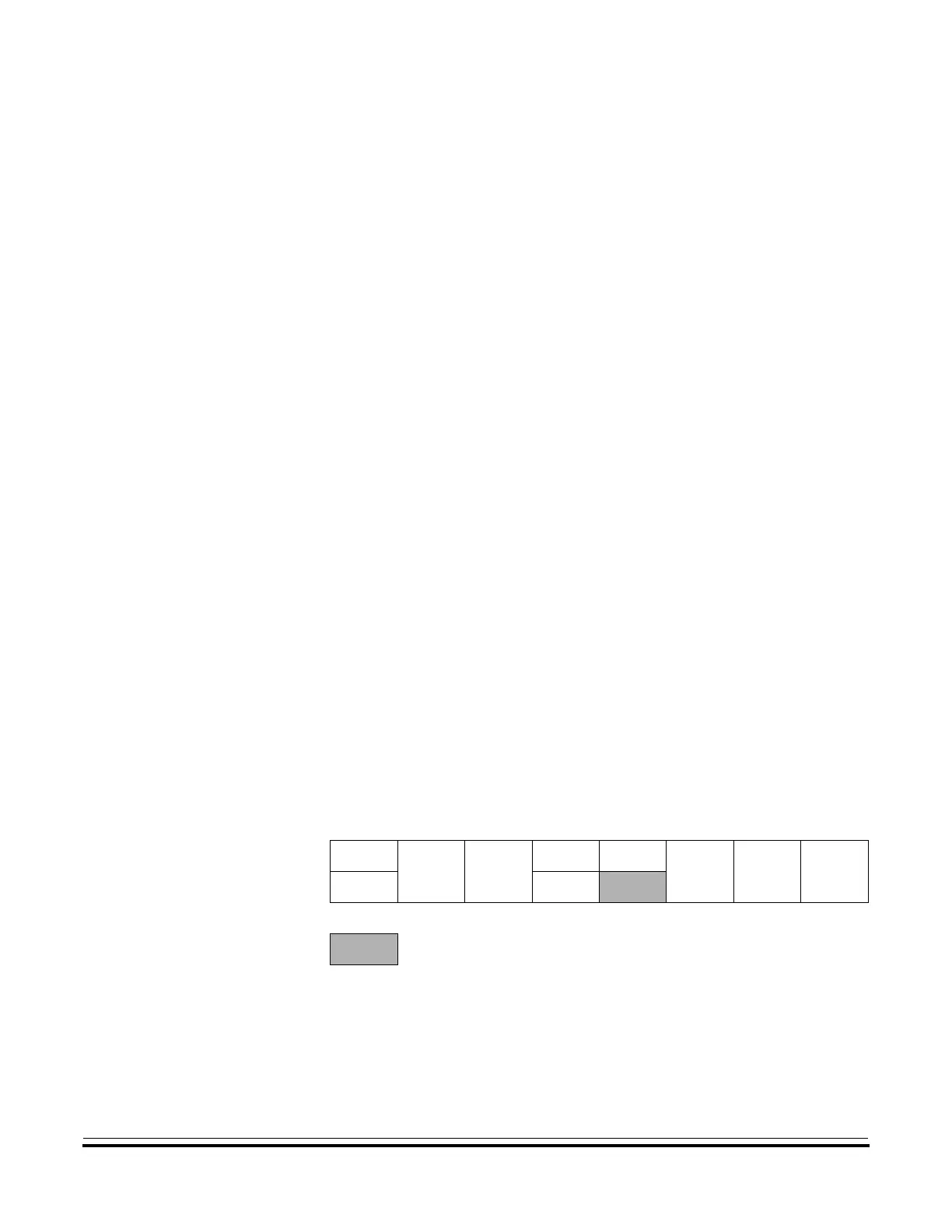

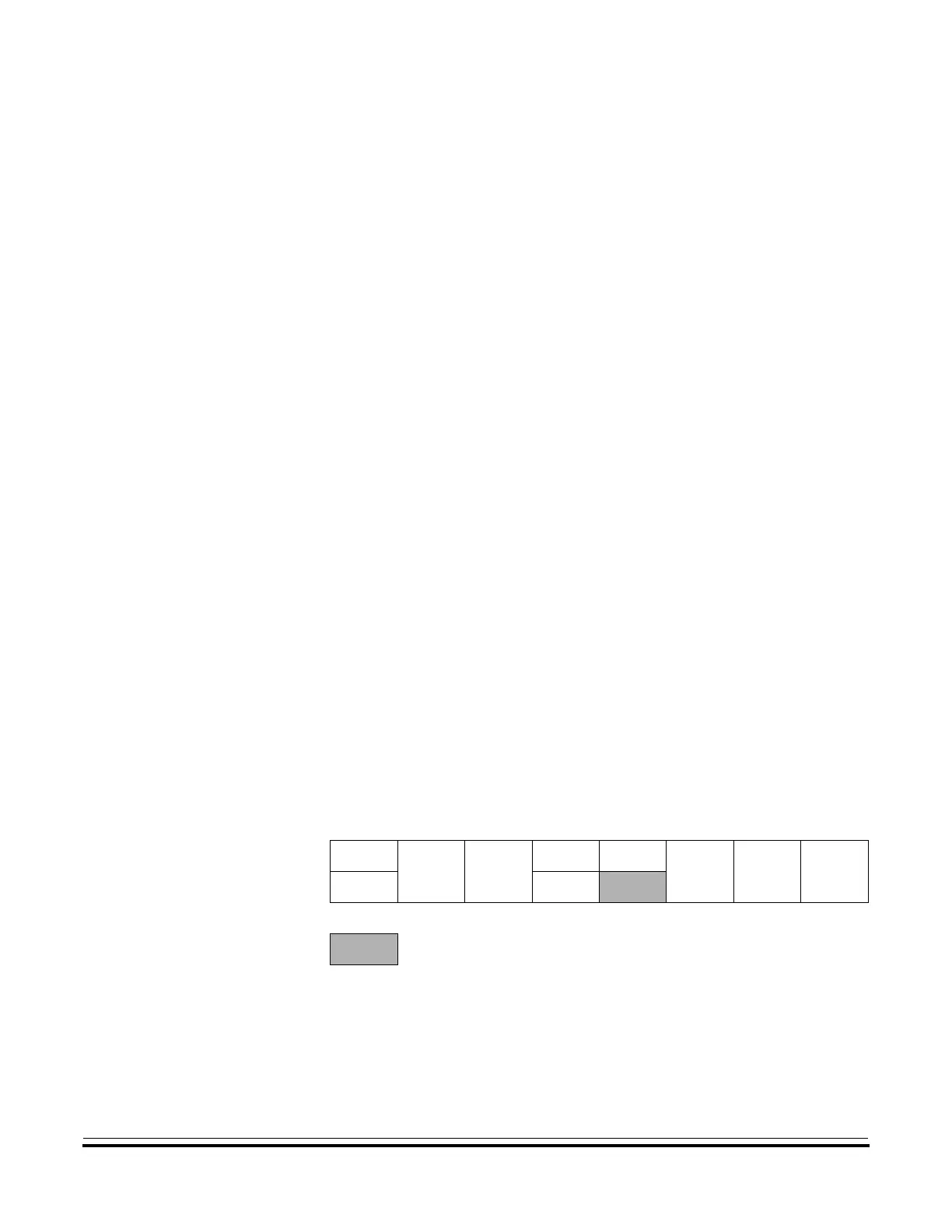

13.7.1 PIT Status and Control Register

The PIT status and control register does the following:

• Enables PIT interrupt

• Flags PIT overflows

• Stops the PIT counter

• Resets the PIT counter

• Prescales the PIT counter clock

Address: $004B

Bit 7 654321Bit 0

Read: POF

POIE PSTOP

00

PPS2 PPS1 PPS0

Write: 0 PRST

Reset:

00100000

=

Unimplemented

Figure 13-3. PIT Status and Control Register (PSC)

Loading...

Loading...