Timer Interface Module B (TIMB)

Technical Data MC68HC908AB32 — Rev. 1.0

218 Timer Interface Module B (TIMB) MOTOROLA

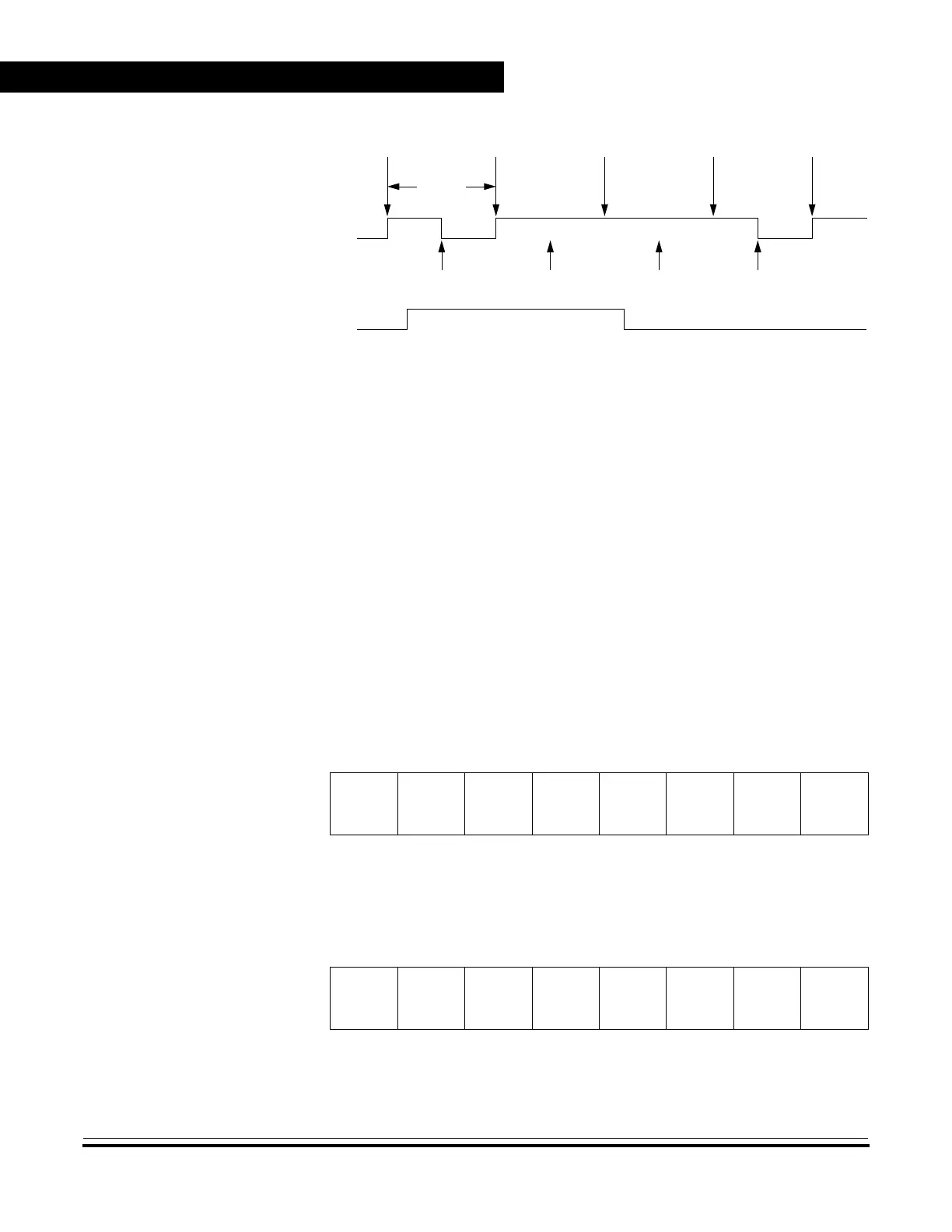

Figure 12-13. CHxMAX Latency

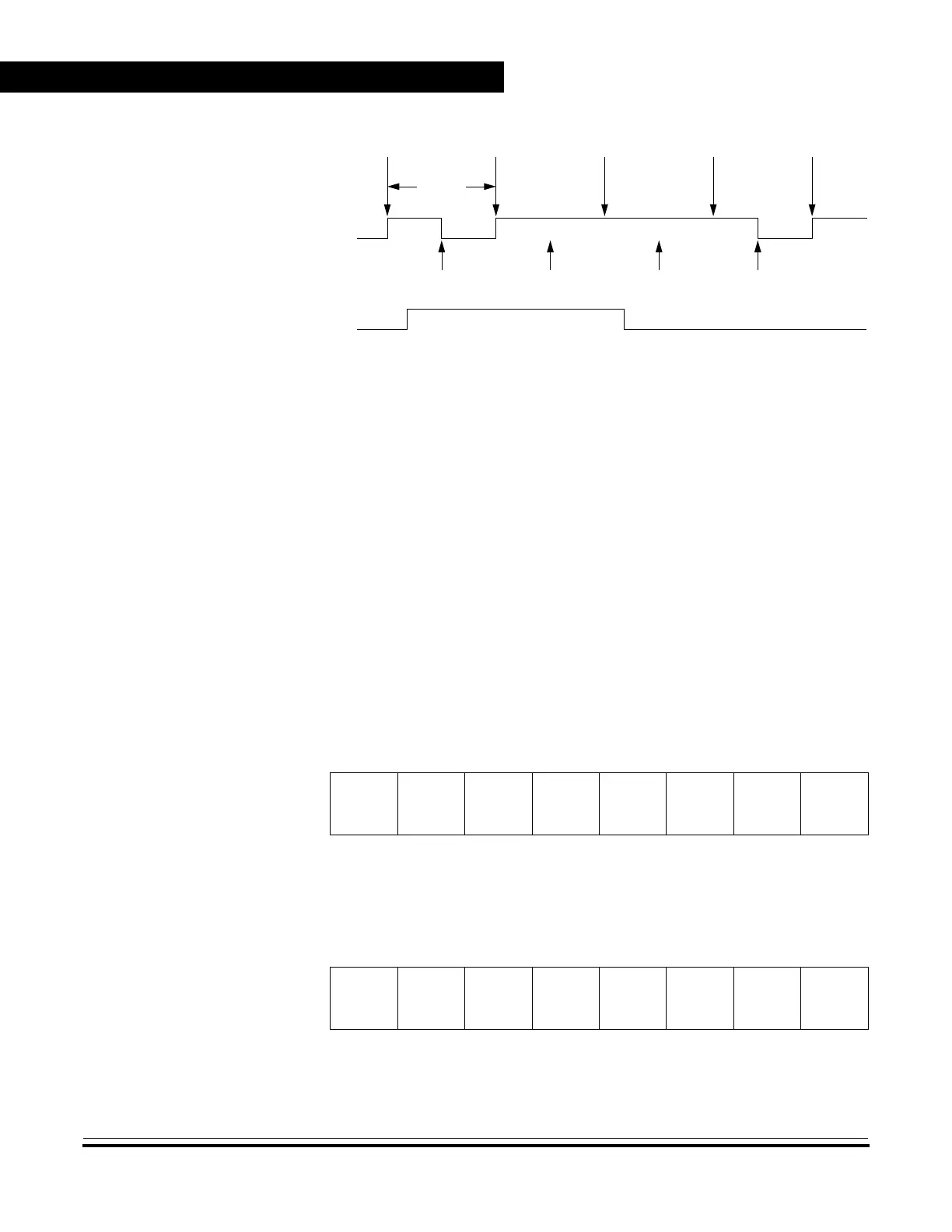

12.10.5 TIMB Channel Registers

These read/write registers contain the captured TIMB counter value of

the input capture function or the output compare value of the output

compare function. The state of the TIMB channel registers after reset is

unknown.

In input capture mode (MSxB:MSxA = 0:0), reading the high byte of the

TIMB channel x registers (TBCHxH) inhibits input captures until the low

byte (TBCHxL) is read.

In output compare mode (MSxB:MSxA ≠ 0:0), writing to the high byte of

the TIMB channel x registers (TBCHxH) inhibits output compares until

the low byte (TBCHxL) is written.

OUTPUT

OVERFLOW

TBCHx

PERIOD

CHxMAX

OVERFLOW OVERFLOW OVERFLOW OVERFLOW

COMPARE

OUTPUT

COMPARE

OUTPUT

COMPARE

OUTPUT

COMPARE

Address: $0046

Bit 7 654321Bit 0

Read:

Bit 15 14 13 12 11 10 9 Bit 8

Write:

Reset: Indeterminate after reset

Figure 12-14. TIMB Channel 0 Register High (TBCH0H)

Address: $0047

Bit 7 654321Bit 0

Read:

Bit 7 654321Bit 0

Write:

Reset: Indeterminate after reset

Figure 12-15. TIMB Channel 0 Register Low (TBCH0L)

Loading...

Loading...