Computer Operating Properly (COP)

Technical Data MC68HC908AB32 — Rev. 1.0

354 Computer Operating Properly (COP) MOTOROLA

20.3 Functional Description

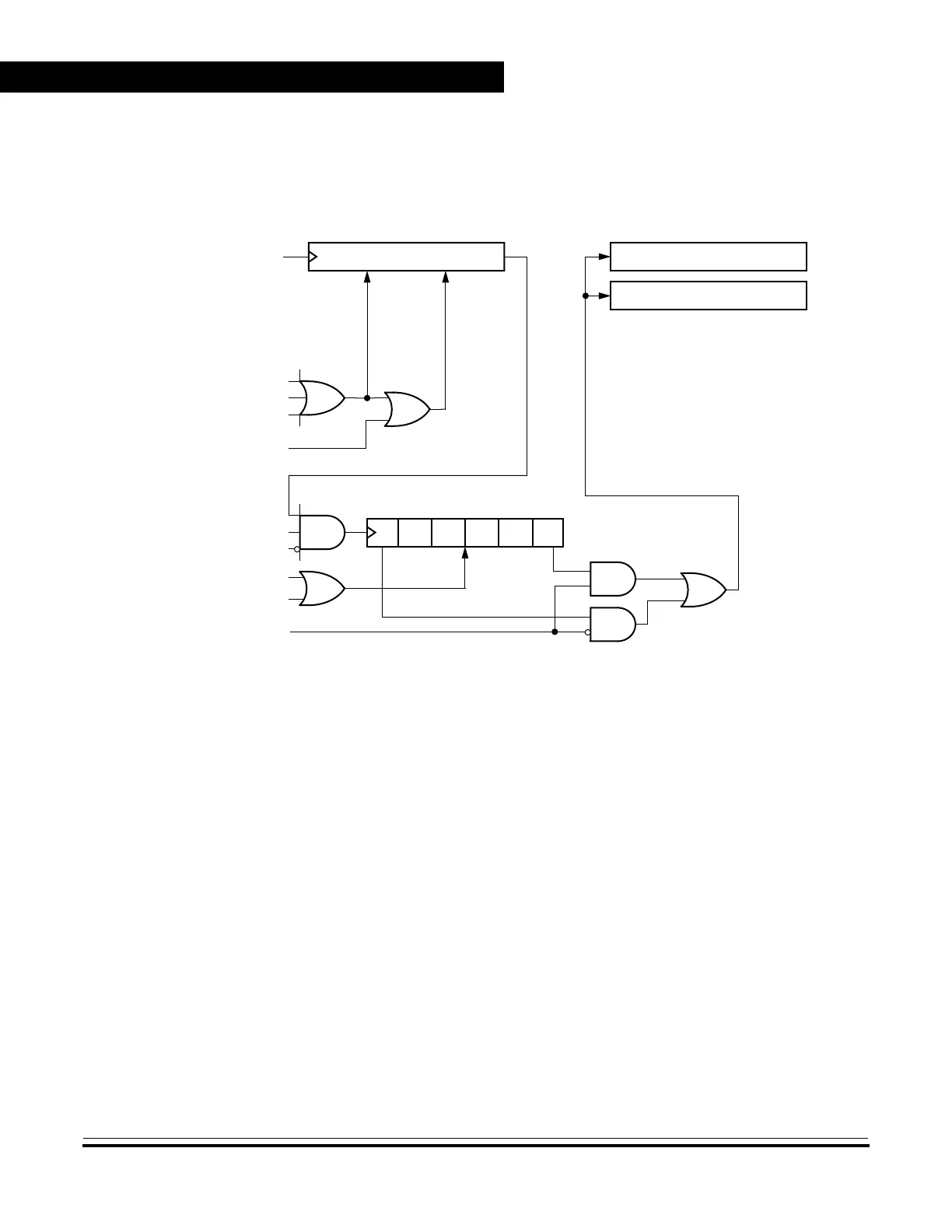

Figure 20-1 shows the structure of the COP module.

Figure 20-1. COP Block Diagram

The COP counter is a free-running 6-bit counter preceded by a 12-bit

prescaler counter. If not cleared by software, the COP counter overflows

and generates an asynchronous reset after 2

18

– 2

4

or 2

13

– 2

4

CGMXCLK cycles, depending on the state of the COP rate select bit,

COPRS, in configuration register 1. With a 2

18

– 2

4

CGMXCLK cycle

overflow option, a 4.9152MHz crystal gives a COP timeout period of

53.3ms. Writing any value to location $FFFF before an overflow occurs

prevents a COP reset by clearing the COP counter and stages 12

through 5 of the prescaler.

NOTE:

Service the COP immediately after reset and before entering or after

exiting stop mode to guarantee the maximum time before the first COP

counter overflow.

COPCTL WRITE

CGMXCLK

RESET VECTOR FETCH

RESET CIRCUIT

RESET STATUS REGISTER

INTERNAL RESET SOURCES

12-BIT COP PRESCALER

CLEAR ALL STAGES

6-BIT COP COUNTER

COP DISABLE

RESET

COPCTL WRITE

CLEAR

COP MODULE

COPEN (FROM SIM)

COP COUNTER

COP CLOCK

COP TIMEOUT

STOP INSTRUCTION

(COPD FROM CONFIG1)

COP RATE SEL

(COPRS FROM CONFIG1)

CLEAR STAGES 5–12

Loading...

Loading...