Programmable Interrupt Timer (PIT)

Technical Data MC68HC908AB32 — Rev. 1.0

228 Programmable Interrupt Timer (PIT) MOTOROLA

13.7.3 PIT Counter Modulo Registers

The read/write PIT modulo registers contain the modulo value for the PIT

counter. When the PIT counter reaches the modulo value, the overflow

flag (POF) becomes set, and the PIT counter resumes counting from

$0000 at the next clock. Writing to the high byte (PMODH) inhibits the

POF bit and overflow interrupts until the low byte (PMODL) is written.

Reset sets the PIT counter modulo registers.

NOTE:

Reset the PIT counter before writing to the PIT counter modulo registers.

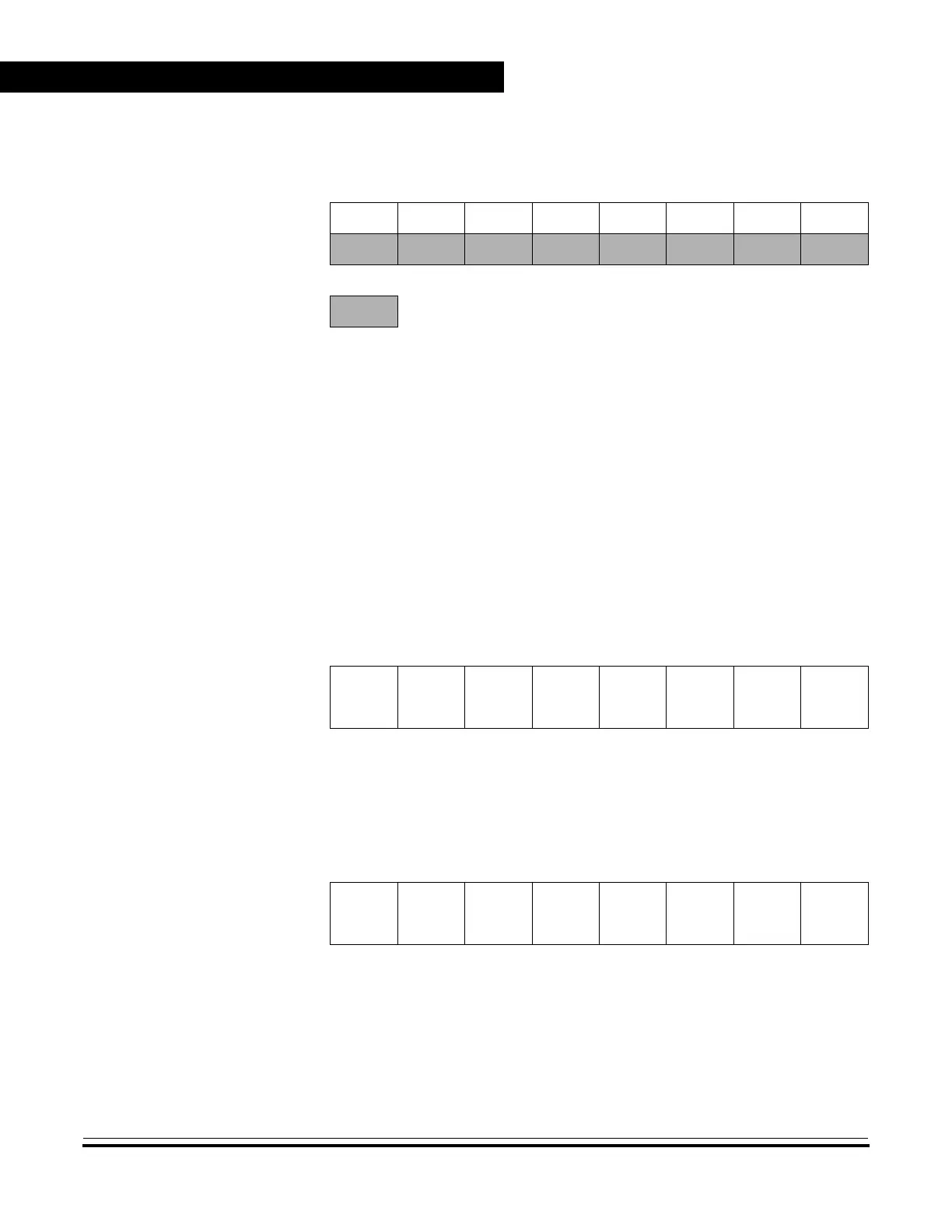

Address: $004D

Bit 7 654321Bit 0

Read: Bit 7 654321Bit 0

Write:

Reset: 00000000

=

Unimplemented

Figure 13-5. PIT Counter Register Low (PCNTL)

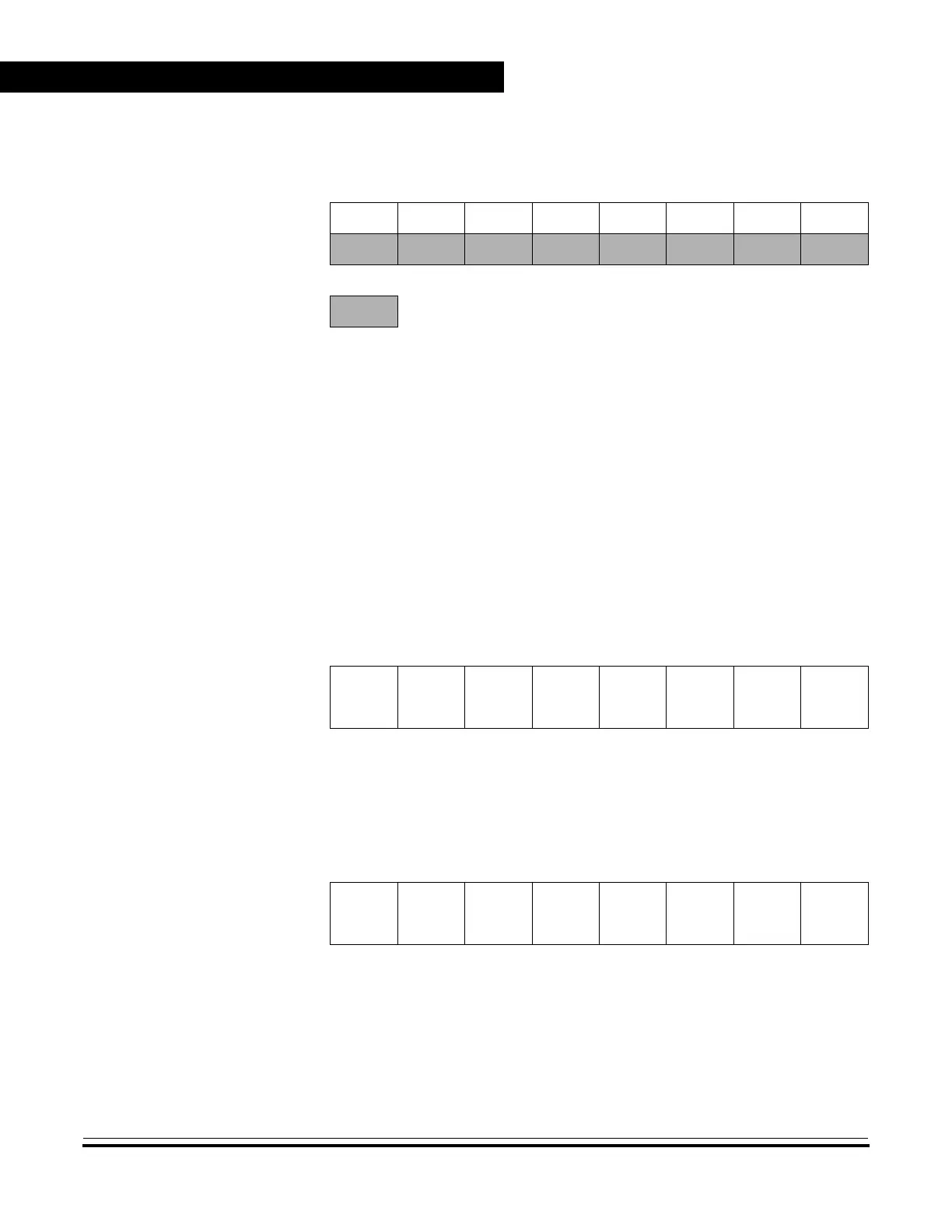

Address: $004E

Bit 7 654321Bit 0

Read:

Bit 15 14 13 12 11 10 9 Bit 8

Write:

Reset: 11111111

Figure 13-6. PIT Counter Modulo Register High (PMODH)

Address: $004F

Bit 7 654321Bit 0

Read:

Bit 7 654321Bit 0

Write:

Reset: 11111111

Figure 13-7. PIT Counter Modulo Register Low (PMODL)

Loading...

Loading...