9-24 Setting the SEL-351P Recloser Control Date Code 990430

SEL-351P Manual Técnico

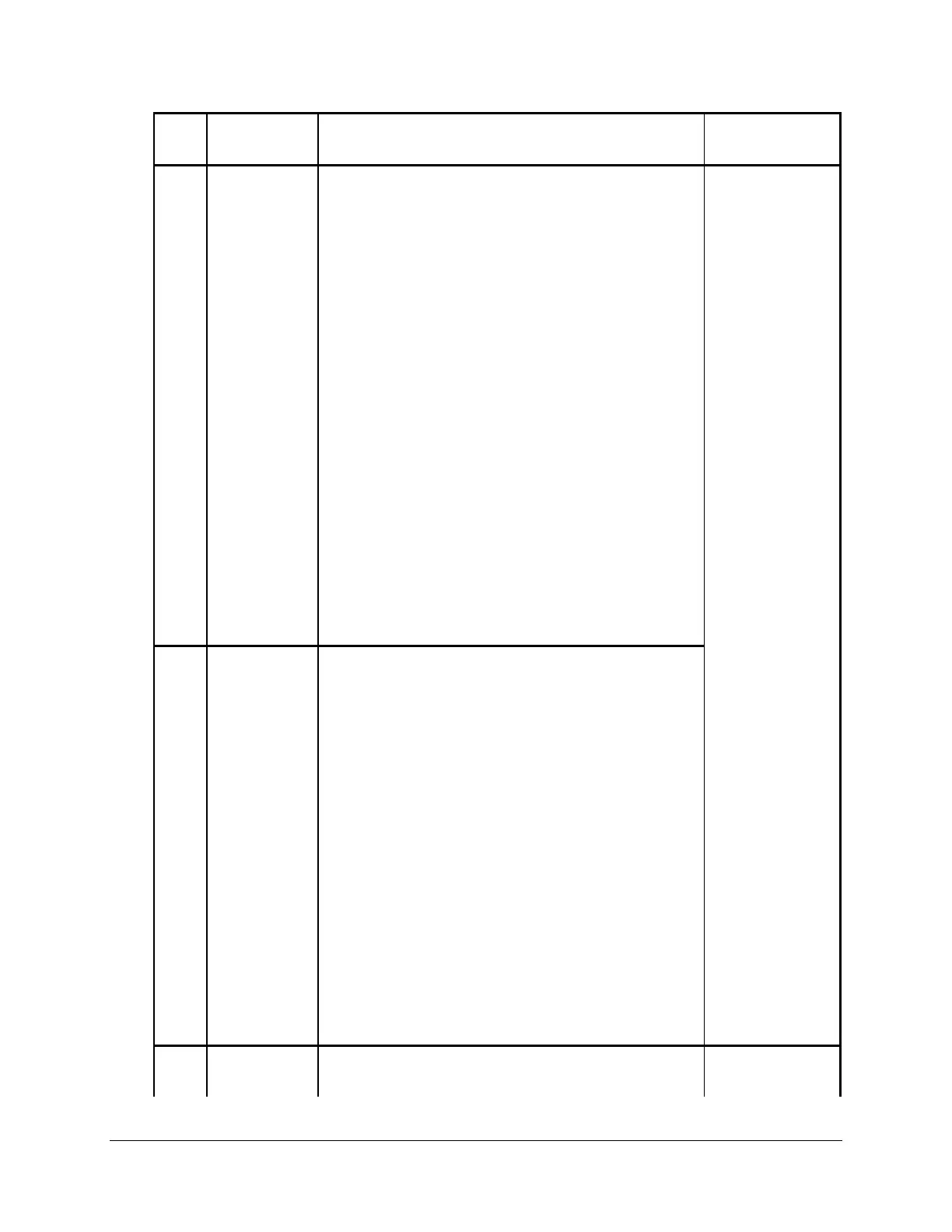

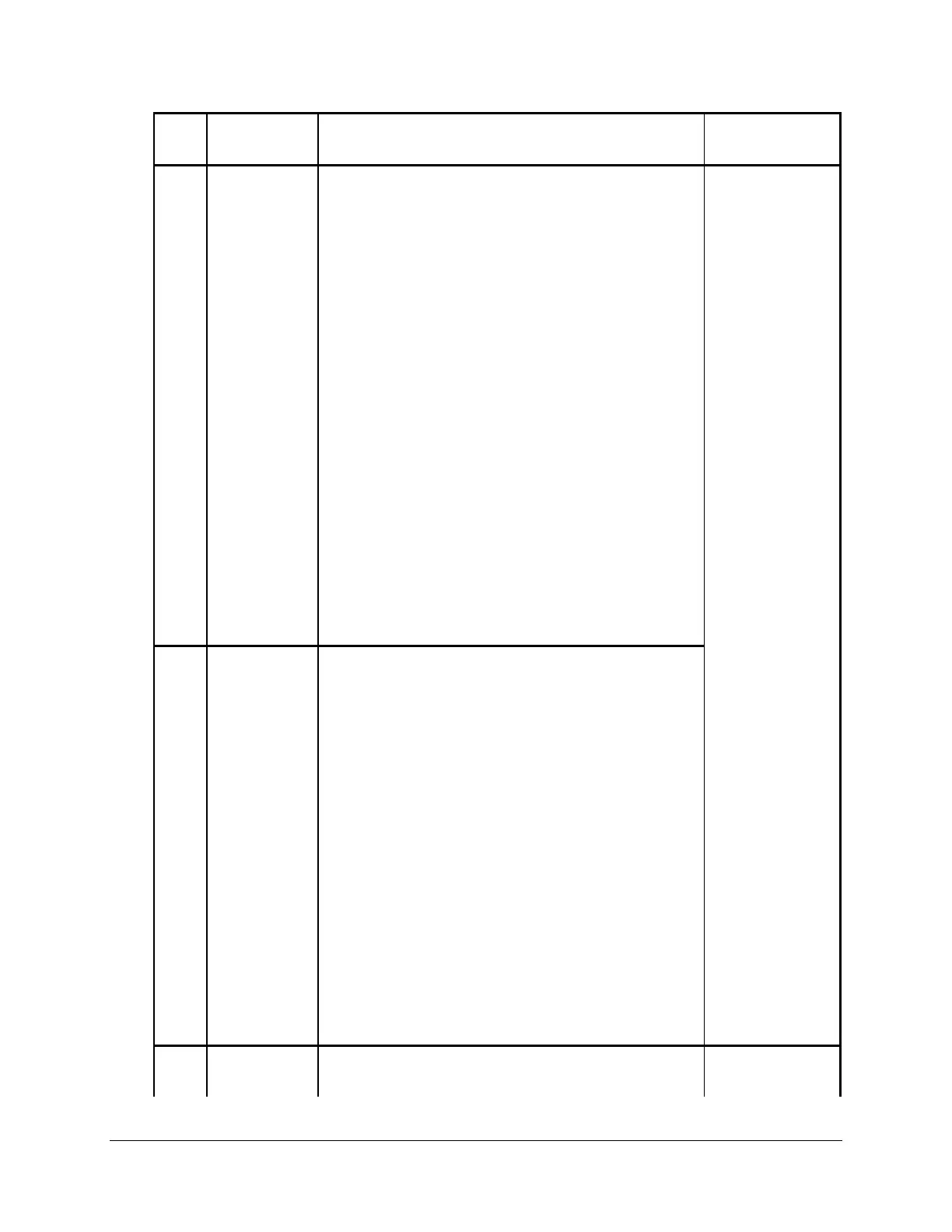

Row

Bit

Definition

Primary

Application

8 50P1 Level 1 phase instantaneous overcurrent element

(= 50A1 + 50B1 + 50C1; see Figure 3.1)

Tripping,

Testing, Control

50P2 Level 2 phase instantaneous overcurrent element

(= 50A2 + 50B2 + 50C2; see Figure 3.1)

50P3 Level 3 phase instantaneous overcurrent element

(= 50A3 + 50B3 + 50C3; see Figure 3.1)

50P4 Level 4 phase instantaneous overcurrent element

(= 50A4 + 50B4 + 50C4; see Figure 3.1)

50N1 Level 1 neutral ground instantaneous overcurrent

element (neutral ground current [channel IN] above

pickup setting 50N1P; see Figure 3.8)

50N2 Level 2 neutral ground instantaneous overcurrent

element (neutral ground current [channel IN] above

pickup setting 50N2P; see Figure 3.8)

50N3 Level 3 neutral ground instantaneous overcurrent

element (neutral ground current [channel IN] above

pickup setting 50N3P; see Figure 3.8)

50N4 Level 4 neutral ground instantaneous overcurrent

element (neutral ground current [channel IN] above

pickup setting 50N4P; see Figure 3.8)

9 67P1 Level 1 phase instantaneous overcurrent element

(derived from 50P1; see Figure 3.3)

67P2 Level 2 phase instantaneous overcurrent element

(derived from 50P2; see Figure 3.3)

67P3 Level 3 phase instantaneous overcurrent element

(derived from 50P3; see Figure 3.3)

67P4 Level 4 phase instantaneous overcurrent element

(derived from 50P4; see Figure 3.3)

67N1 Level 1 neutral ground instantaneous overcurrent

element (derived from 50N1; see Figure 3.8)

67N2 Level 2 neutral ground instantaneous overcurrent

element (derived from 50N2; see Figure 3.8)

67N3 Level 3 neutral ground instantaneous overcurrent

element (derived from 50N3; see Figure 3.8)

67N4 Level 4 neutral ground instantaneous overcurrent

element (derived from 50N4; see Figure 3.8)

10 67P1T Level 1 phase definite-time overcurrent element

67P1T timed out (derived from 67P1; see Figure 3.3)

Tripping

Loading...

Loading...